Æ

## Ontwerp van een geschakelde xDSL versterker in een submicron hoogspanningstechnologie

Design of a Switching xDSL Line Driver in a Submicron High Voltage Technology

Vincent De Gezelle

Promotor: prof. dr. ir. J. Doutreloigne

Proefschrift ingediend tot het behalen van de graad van Doctor in de Ingenieurswetenschappen: Elektrotechniek

Vakgroep Electronica en Informatiesystemen Voorzitter: prof. dr. ir. J. Van Campenhout Faculteit Ingenieurswetenschappen Academiejaar 2008–2009

Ð

⊕

"doctoraat VDG" — 2009/8/13 — 11:30 — page 2 — #2

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

Æ

## Ontwerp van een geschakelde xDSL versterker in een submicron hoogspanningstechnologie

Design of a Switching xDSL Line Driver in a Submicron High Voltage Technology

Vincent De Gezelle

Promotor: prof. dr. ir. J. Doutreloigne

Proefschrift ingediend tot het behalen van de graad van Doctor in de Ingenieurswetenschappen: Elektrotechniek

Vakgroep Electronica en Informatiesystemen Voorzitter: prof. dr. ir. J. Van Campenhout Faculteit Ingenieurswetenschappen Academiejaar 2008–2009

Ð

⊕

"doctoraat VDG" — 2009/8/13 — 11:30 — page 4 — #4

$\oplus$

$\oplus$

$\oplus$

⊕

ISBN 978-90-8578-300-8

NUR 959

$\oplus$

$\oplus$

$\oplus$

$\oplus$

Wettelijk depot: D/2009/10.500/58

$\oplus$

$\oplus$

$\oplus$

Promotor:

$\oplus$

$\oplus$

$\oplus$

$\oplus$

Prof. dr. ir. J. Doutreloigne

Onderzoeksgroep CMST Vakgroep Electronica en Informatiesystemen Technologiepark 914A B-9052 Zwijnaarde

"doctoraat VDG" — 2009/8/13 — 11:30 — page 6 — #6

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

## Dankwoord

Plots zit ik daar dan, verstand op nul, blik op oneindig en een nog warme stapel vers afgedrukt papier voor mijn neus. De vaststelling dat de georganiseerde chaos die ik "bureau" noem toch eens wat opgeruimd moet worden, onmiddellijk gevolgd door de gedachte dat ik dan impulsief en met grenzeloos enthousiasme dingen weg zal smijten die ik achteraf toch nog nodig blijk te hebben. De reden voor dit alles? Na acht jaar ligt hier eindelijk een schriftelijke samenvatting van een belangrijk deel van het onderzoek en projectwerk dat ik in die periode verricht heb. Dit zou echter nooit mogelijk geweest zijn zonder de steun van een heleboel mensen.

Als eerste zou ik prof. André Van Calster willen bedanken om mij als pas afgestudeerd ingenieur op te nemen in de TFCG/CMST familie en ons van tijd tot tijd te verwennen met een diner of een BBQ. Daarnaast heeft natuurlijk ook mijn promotor, prof. Jan Doutreloigne, een belangrijke rol gespeeld, door regelmatig eens wat licht te doen schijnen in de tunnel, dit proefschrift te lezen en de nodige kritische opmerkingen te formuleren.

Dank ook aan alle collega's en ex-collega's, zonder hen was het hier maar saai geweest. Een aantal van hen zou ik toch extra willen bedanken. Jean, om de settings voor mijn designomgeving op punt te helpen zetten en mij te introduceren in een wondere wereld genaamd "Cadence". Ronny en Michiel om mij te assisteren bij de meest waanzinnige Unix-problemen en Wim om Cadence draaiende te houden. Dieter, om mij af en toe binnen te smokkelen in de cleanroom als ik weer eens microscoopfotookes nodig had van deze of gene chip. Björn voor al het wirebonden en het fijnere soldeerwerk en Lieven voor de Mentor-support.

Mijn bureaugenoten mogen natuurlijk ook niet ontbreken. Benoit voor de eerste hulp bij speciale devices en Ann om altijd opgewekt te zijn. Zangvogel Stefaan, omdat er toch iemand wat leven in de designerbrouwerij moet brengen en Pieter en Dominique om te allen tijde de kalmte te bewaren. Jodie, bedankt om af en toe eens een lastige vraag te stellen. Hopelijk heb je iets aan dit boek.

Verder wens ik ook enkele mensen van Alcatel-Lucent te bedanken. Marnix, zonder jou zou het financiële plaatje er ongetwijfeld anders uitgezien hebben. Eddy, bedankt voor de technische support, het ter beschikking stellen van een pak interessante documenten en de verhelderende uitleg over alles wat met telefonie te maken heeft. Also a special thanks to the people of ETCA Charleroi to allow me to confiscate several power supplies, a signal generator and their spectrum analyzer for my final measurements. Philippe, Karim, Pierre-Gilles and Stephanie, thank you very much.

Naast het professionele gedeelte, zijn er natuurlijk nog mensen die mij, elk op hun manier, tijdens mijn vrije tijd gesteund hebben. De muzikanten van het ter ziele gegane Tempi Misti en opvolger Guso, door wie ik verplicht ben af en toe mijn cello nog eens af te stoffen. De "Insiders", om te bewijzen dat er behalve whine-surfers ook nog windsurfers zijn die effectief gaan varen. Daarnaast zijn er ook nog "de mannen van Brugge" die mij af en toe meetweefelden om een ander stukje België onveilig te gaan maken.

Als laatste, maar daarom zeker niet minder belangrijk, zijn er nog mijn ouders en zus. Bedankt voor alle kansen die ik gekregen heb, voor de financiële ondersteuning, de goede raad, om mij overal naartoe te voeren of de auto te lenen, ook al wordt die dan steevast mishandeld door tientallen kilo's aan plastic en carbon op het dak te stouwen, voor al die dingen die evident lijken maar het niet zijn. Charlotte, bedankt om te bewijzen dat een viool best wel mooi kan klinken en om mij te verblijden met weetjes zoals het aantal verschillende noten dat koolmezen en pimpelmezen kunnen produceren.

Bedankt voor alles!

Vincent De Gezelle

Gent, 12 augustus 2009

ii

$\oplus$

$\oplus$

$\oplus$

# Contents

$\oplus$

$\oplus$

$\oplus$

| 1 | Intr | oduction                             | 1        |

|---|------|--------------------------------------|----------|

|   | 1.1  | Wire line communication              | 1        |

|   |      | 1.1.1 Rise of the network            | 1        |

|   |      | 1.1.2 Extending the applications     | 2        |

|   |      | 1.1.3 Some properties of xDSL        | 2        |

|   | 1.2  | Context and goal of this work        | 4        |

|   | 1.3  | Outline                              | 7        |

| 2 | Corr | cont and marifaction                 | 11       |

| 2 |      | cept and verification                | 11<br>11 |

|   | 2.1  | Preliminary considerations           |          |

|   | 2.2  | Technology overview                  | 14       |

|   |      | DMOS transistors                     | 14       |

|   |      | MOS transistors                      | 14       |

|   |      | Capacitors                           | 15<br>15 |

|   | 2.2  | Resistors                            | 15       |

|   | 2.3  | Zeroth order                         | 16       |

|   |      | 2.3.1 Schematics and simulations     | 16       |

|   |      | Output stage                         | 16       |

|   |      |                                      | 20       |

|   |      | Full simulation                      | 25       |

|   | 0.4  | 2.3.2 Layout and measurement results | 30       |

|   | 2.4  | First order                          | 34       |

|   |      | 2.4.1 Schematics and simulations     | 34       |

|   |      | Opamp and integrator                 | 34       |

|   |      |                                      | 38       |

|   |      | Biasing circuit                      | 41       |

|   |      | Output stage                         | 45       |

|   |      | Full simulation                      | 46       |

|   |      | 2.4.2 Layout and measurement results | 55       |

|   |      | Reference circuit                    | 55       |

|   |      | Amplifiers                           | 55       |

|   | 2.5  | Conclusion                           | 61       |

iv

$\oplus$

$\oplus$ —

$\oplus$

## CONTENTS

$\oplus$

$\oplus$

$\oplus$

| 3 | The | ory of o | operation                       | 65  |

|---|-----|----------|---------------------------------|-----|

|   | 3.1 | Introd   | luction                         | 65  |

|   | 3.2 | Descri   | ibing functions linearization   | 66  |

|   |     | 3.2.1    | Small and large signals         | 66  |

|   |     | 3.2.2    | Large signal approximation      | 67  |

|   |     | 3.2.3    | An example                      | 70  |

|   |     |          | Offset                          | 70  |

|   |     |          | Sinewave                        | 70  |

|   |     |          | Full response                   | 72  |

|   |     | 3.2.4    | Sinusoidal input signals        | 72  |

|   |     |          | A single sinusoid               | 72  |

|   |     |          | A sinusoid with other signals   | 74  |

|   |     |          | Exponential transfer revisited  | 74  |

|   |     | 3.2.5    | Limit cycle calculation         | 75  |

|   | 3.3 | Distor   | tion calculation                | 76  |

|   |     | 3.3.1    | Zeroth and first order loop     | 77  |

|   |     | 3.3.2    | Second order loop               | 80  |

|   |     | 3.3.3    | Third order loop                | 81  |

|   | 3.4 | Nume     | erical verification             | 82  |

|   |     | 3.4.1    | First order loop                | 82  |

|   |     |          | Oscillating frequency           | 82  |

|   |     |          | Third order harmonic distortion | 83  |

|   |     |          | Simulation                      | 83  |

|   |     | 3.4.2    | 10MHz second order loop         | 86  |

|   |     |          | Oscillating frequency           | 86  |

|   |     |          | Third order harmonic distortion | 87  |

|   |     |          | Simulation                      | 88  |

|   |     | 3.4.3    | 30MHz second order loop         | 91  |

|   |     | 3.4.4    | Third order loop                | 94  |

|   |     |          | Oscillating frequency           | 94  |

|   |     |          | Third order harmonic distortion | 94  |

|   |     |          | Simulation                      | 95  |

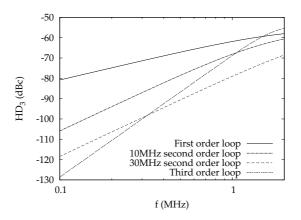

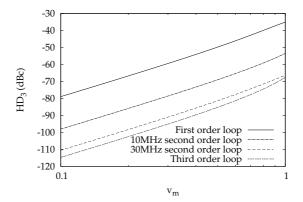

|   |     | 3.4.5    | Discussion                      | 98  |

|   |     |          | Limit cycle frequency           | 98  |

|   |     |          | Third order harmonic distortion | 98  |

|   |     |          | What about MTPR?                | 101 |

|   | 3.5 | Concl    | usion                           | 101 |

| 4 | Des | ignino   | the loop                        | 105 |

| - | 4.1 |          | •                               | 105 |

|   | 4.2 |          | ology overview                  |     |

|   |     | 4.2.1    |                                 | 106 |

|   |     | 4.2.2    | MOS transistors                 |     |

|   |     |          |                                 |     |

"doctoraat VDG" — 2009/8/13 — 11:30 — page v — #11

## CONTENTS

5

$\oplus$

$\oplus$

$\oplus$

$\oplus$

|      | 4.2.3   | Capacitors                            | . 107 |

|------|---------|---------------------------------------|-------|

|      | 4.2.4   | Resistors                             |       |

| 4.3  | Buildi  | ng blocks                             | . 108 |

|      | 4.3.1   | Öpamps                                | . 108 |

|      |         | Integrator                            |       |

|      |         | Voltage follower                      |       |

|      |         | Biasing circuit                       | . 118 |

|      | 4.3.2   | Comparator                            | . 120 |

|      | 4.3.3   | Output stage                          |       |

|      | 4.3.4   | Time delay, level shifter and buffers |       |

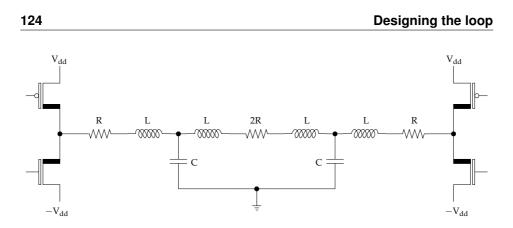

|      | 4.3.5   | Passive filter-divider                |       |

|      |         | First order loop                      |       |

|      |         | 10MHz second order loop               |       |

|      |         | 30MHz second order loop               |       |

|      |         | Third order loop                      |       |

| 4.4  | First o | rder system                           |       |

| 4.5  |         | z second order system                 |       |

| 4.6  |         | z second order system                 |       |

| 4.7  |         | order system                          |       |

| 4.8  |         | d order system with independent loops |       |

| 4.9  |         | t considerations                      |       |

|      | 4.9.1   | Interconnection                       |       |

|      | 4.9.2   | Components                            |       |

| 4.10 | Conclu  | usion                                 |       |

|      |         |                                       |       |

|      | surem   |                                       | 151   |

| 5.1  |         | uction                                |       |

| 5.2  |         | measurements                          |       |

|      | 5.2.1   | First order system                    |       |

|      |         | DC response                           |       |

|      |         | AC response                           |       |

|      |         | MTPR response                         |       |

|      | 5.2.2   | 10MHz second order system             |       |

|      |         | DC response                           |       |

|      |         | AC response                           |       |

|      |         | MTPR response                         |       |

|      | 5.2.3   | 30MHz second order system             |       |

|      |         | DC response                           | . 159 |

|      |         | AC response                           |       |

|      |         | MTPR response                         |       |

|      | 5.2.4   | Third order system                    |       |

|      |         | DC response                           | . 164 |

|      |         | AC response                           | . 164 |

$\oplus$

$\oplus$

$\oplus$

## CONTENTS

$\oplus$

$\oplus$

$\oplus$

$\oplus$

|   |     |         | MTPR response                                  |

|---|-----|---------|------------------------------------------------|

|   |     | 5.2.5   | Second order system with independent loops     |

|   |     |         | DC response                                    |

|   |     |         | AC response                                    |

|   |     |         | MTPR response                                  |

|   | 5.3 | Troub   | leshooting                                     |

|   | 5.4 | Final 1 | measurements                                   |

|   |     | 5.4.1   | First order system                             |

|   |     |         | DC response                                    |

|   |     |         | AC response                                    |

|   |     |         | MTPR response                                  |

|   |     | 5.4.2   | 10MHz second order system 184                  |

|   |     |         | DC response                                    |

|   |     |         | AC response                                    |

|   |     |         | MTPR response                                  |

|   |     | 5.4.3   | 30MHz second order system                      |

|   |     |         | DC response                                    |

|   |     |         | AC response                                    |

|   |     |         | MTPR response                                  |

|   |     | 5.4.4   | Third order system                             |

|   |     |         | DC response                                    |

|   |     |         | AC response                                    |

|   |     | - 4 -   | MTPR response                                  |

|   |     | 5.4.5   | Second order system with independent loops 192 |

|   |     |         | DC response                                    |

|   |     |         | AC response                                    |

|   |     | Const   | MTPR response                                  |

|   | 5.5 | Conci   | usion                                          |

| 6 | Con | clusior | ns and outlook 203                             |

| ÷ | 6.1 |         | achievements                                   |

|   | 6.2 |         | e work                                         |

|   | 6.3 | Feasib  | ility and extensibility                        |

vi

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

# List of Tables

$\oplus$

$\oplus$

$\oplus$

$\oplus$

| 2.1  | Key characteristics of I <sup>2</sup> T100 DMOS devices | 14  |

|------|---------------------------------------------------------|-----|

| 2.2  | Key characteristics of I <sup>2</sup> T100 MOS devices  | 15  |

| 2.3  | Key characteristics of I <sup>2</sup> T100 capacitors   | 15  |

| 2.4  | Key characteristics of I <sup>2</sup> T100 resistors    | 16  |

| 2.5  | Transistor dimensions of level shifter and buffer       | 18  |

| 2.6  | Transistor dimensions of the delay circuit              | 22  |

| 2.7  | Transistor dimensions of the comparator                 | 23  |

| 2.8  | Delay times of the comparator                           | 25  |

| 2.9  | Summary of simulation results                           | 28  |

| 2.10 | Power dissipation of the single ended amplifier         | 28  |

|      | Maximum $dV/dt$ capability of the DMOS switches used    | 29  |

|      | Calculated dimensions of the opamp transistors          | 37  |

|      | Optimized component dimensions of the opamp             | 38  |

| 2.14 | Simulation results of the opamp                         | 39  |

| 2.15 | Transistor dimensions of the comparator                 | 41  |

| 2.16 | Delay times of the comparator                           | 41  |

|      | Transistor dimensions of the reference circuit          | 45  |

| 2.18 | Voltages and currents from the reference circuit        | 46  |

| 2.19 | Transistor dimensions of level shifter and buffer       | 47  |

| 2.20 | Transistor dimensions of the delay circuit              | 48  |

| 2.21 | Summary of the simulation results                       | 52  |

|      | Summary of the calculated results                       | 54  |

| 2.23 | Measured voltages from the reference circuit            | 56  |

|      | Comparison of measurement results                       | 61  |

|      |                                                         |     |

| 3.1  | Bernoulli numbers                                       | 79  |

| 3.2  | Calculated and simulated limit cycle frequencies        | 98  |

| 3.3  | Simulated MTPR                                          | 101 |

| 4.1  |                                                         | 100 |

| 4.1  | Key characteristics of $I^3$ T80 DMOS devices           |     |

| 4.2  | Key characteristics of $I^3$ T80 MOS devices            |     |

| 4.3  | Key characteristics of $I^3T80$ capacitors              | 107 |

| 4.4  | Key characteristics of I <sup>3</sup> T80 resistors     | 108 |

## LIST OF TABLES

$\oplus$

$\oplus$

$\oplus$

$\oplus$

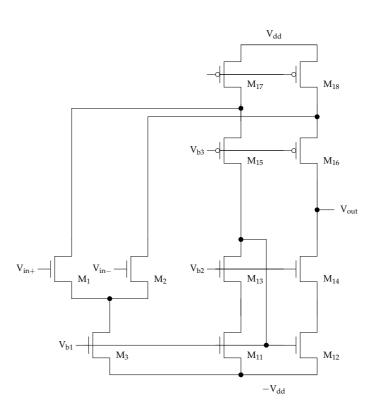

| 4.5  | Final dimensions of the opamp 111                                  |

|------|--------------------------------------------------------------------|

| 4.6  | Final dimensions of the opamp 115                                  |

| 4.7  | Transistor dimensions of the biasing circuit                       |

| 4.8  | Transistor dimensions of the basic comparator 121                  |

| 4.9  | Transistor dimensions of the comparator                            |

| 4.10 | Normalized values for a third order Chebychev low pass filter with |

|      | 1dB ripple                                                         |

| 4.11 | Dimensions of the output transistors                               |

| 4.12 | Transistor dimensions of the delay circuit                         |

| 4.13 | Transistor dimensions of the low to high level shifter 129         |

| 4.14 | Transistor dimensions of the high to low level shifter 129         |

| 4.15 | Dimensions of the first order loop filter components               |

| 4.16 | Dimensions of the 10MHz second order loop filter components 132    |

| 4.17 | Dimensions of the 30MHz second order loop filter components 133    |

| 4.18 | Dimensions of the third order loop filter components               |

| 4.19 | Summary of the calculated efficiencies                             |

|      |                                                                    |

| 5.1  | Maximum saturation voltage at process corners                      |

| 5.2  | Summary of both sets of measurements on all five circuits 200      |

#### viii

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

# List of Figures

$\oplus$

$\oplus$

$\oplus$

$\oplus$

| 1.1  | Simplified diagram of telephone interconnection                   | 3        |

|------|-------------------------------------------------------------------|----------|

| 1.2  | Principle of DMT encoding                                         | 3        |

| 1.3  | Frequency and time domain representation of a DMT encoded         |          |

|      | signal                                                            | 4        |

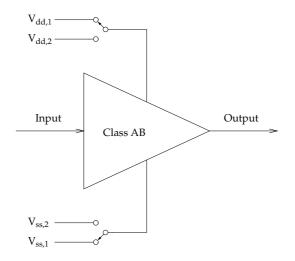

| 1.4  | Simplified diagram of a class G amplifier using multiple supply   |          |

|      | voltages                                                          | 5        |

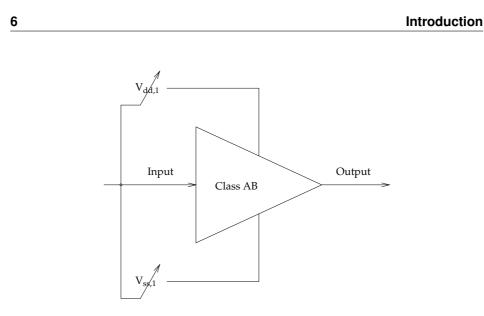

| 1.5  | Simplified diagram of a class G amplifier using a variable supply |          |

|      | voltage                                                           | 6        |

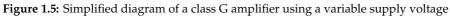

| 1.6  | Block diagram and corresponding waveforms of a basic PWM          |          |

|      | amplifier                                                         | 6        |

| 1.7  | Example of an asynchronous mixed class AB and D amplifier         | 7        |

| 1.8  | Block diagram of an asynchronous class D amplifier                | 8        |

| 0.1  | Plade discourse of an array damage along Descalification          | 10       |

| 2.1  | Block diagram of an asynchronous class D amplifier                | 12       |

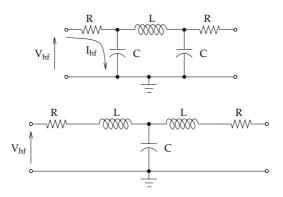

| 2.2  | IT versus T output filter topology                                | 13       |

| 2.3  | More detailed diagram of the asynchronous class D amplifier       | 13       |

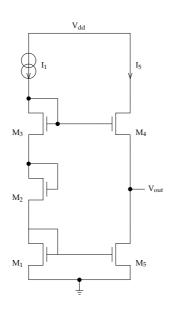

| 2.4  | Schematic of the high voltage output stage                        | 17       |

| 2.5  | Simulation of the high voltage output stage                       | 17       |

| 2.6  | Schematic of the level shifter with buffer                        | 18       |

| 2.7  | Simulation of the level shifter with buffer                       | 19       |

| 2.8  | Illustration of turn-on in DMOS transistors                       | 19       |

| 2.9  | Schematic of the delay circuit                                    | 20       |

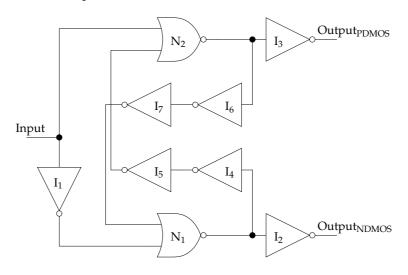

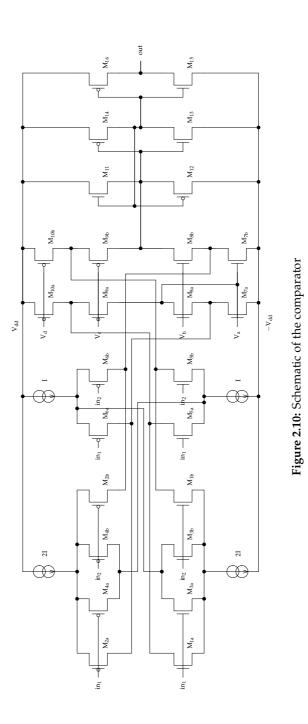

| 2.10 | Schematic of the comparator                                       | 21       |

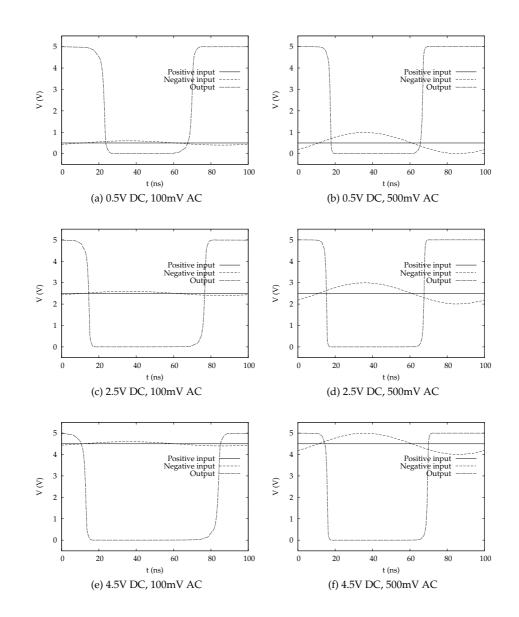

| 2.11 | Simulation of the comparator                                      | 24       |

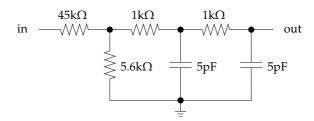

| 2.12 | Schematic of the loop filter                                      | 25       |

| 2.13 | Simulated output of single ended amplifier @ 200kHz reference     | •        |

|      | signal                                                            | 26       |

| 2.14 | Simulated spectrum of single ended amplifier @ 200kHz refer-      | •        |

|      | ence signal                                                       | 26       |

| 2.15 | Simulated output of balanced amplifier @ 200kHz reference signal  | 27       |

| 2.16 | Simulated spectrum of balanced amplifier @ 200kHz reference       | <b>-</b> |

|      | signal                                                            | 27       |

| 2.17 | Simulated gate and output signals of the output stage             | 29       |

$\oplus$

$\oplus$

$\oplus$

$\oplus$

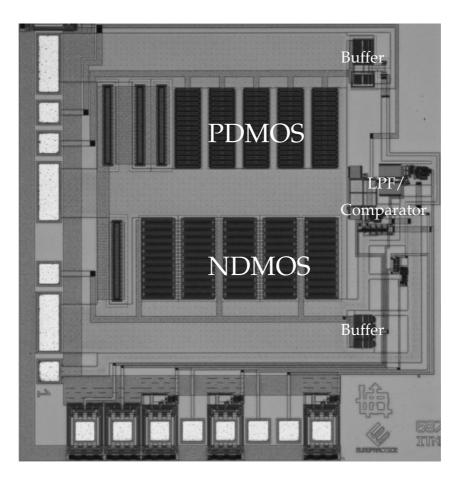

| 2.18 | Die photograph of the amplifier processed                         | 31 |

|------|-------------------------------------------------------------------|----|

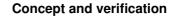

| 2.19 | Measured and ideal output of the asynchronous switching am-       |    |

|      | plifier                                                           | 32 |

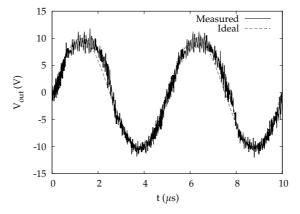

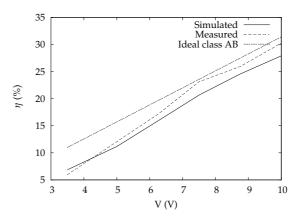

| 2.20 | Efficiency of the asynchronous switching amplifier                | 32 |

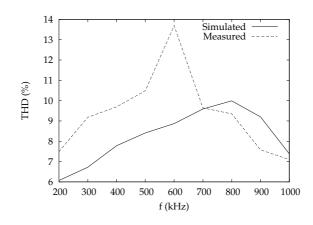

| 2.21 | THD of the asynchronous switching amplifier                       | 33 |

| 2.22 | Efficiency of the asynchronous switching amplifier versus ampli-  |    |

|      | tude                                                              | 33 |

| 2.23 | Block diagram of the modified balanced asynchronous class D       |    |

|      | amplifier                                                         | 34 |

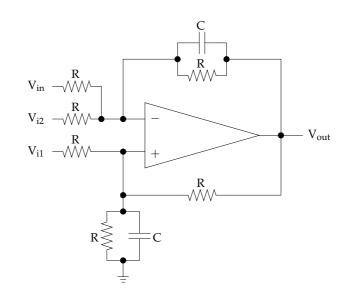

| 2.24 | Integrator circuit                                                | 35 |

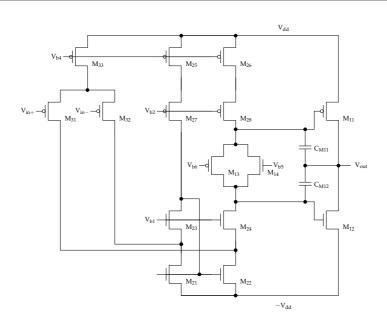

| 2.25 | Schematic of the opamp                                            | 36 |

| 2.26 | Simulated amplitude and phase of the opamp                        | 38 |

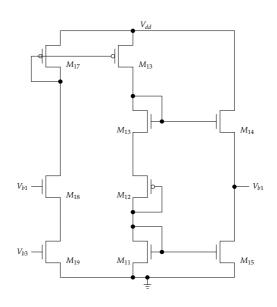

| 2.27 | Schematic of the comparator                                       | 39 |

| 2.28 | Simulation of the comparator                                      | 40 |

| 2.29 | Diagram of the basic voltage reference                            | 42 |

| 2.30 | Schematic of the biasing circuit                                  | 43 |

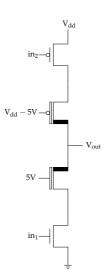

| 2.31 | Diagram of the cascode output stage                               | 47 |

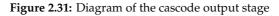

| 2.32 | Schematic of the divider                                          | 48 |

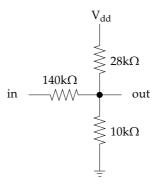

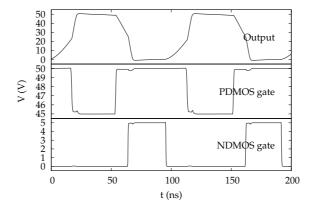

| 2.33 | Simulation of DMOS in and outputs, basic version                  | 49 |

| 2.34 | Simulation of DMOS in and outputs, cascode version                | 49 |

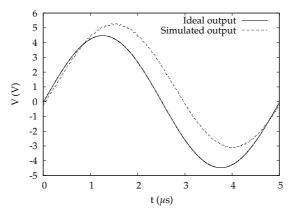

| 2.35 | Simulated output of the basic amplifier @ 200kHz reference signal | 50 |

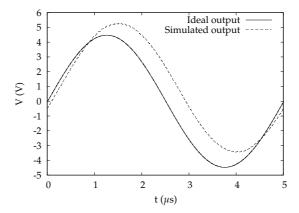

| 2.36 | Simulated output of the cascode amplifier @ 200kHz reference      |    |

|      | signal                                                            | 50 |

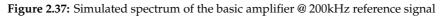

| 2.37 | Simulated spectrum of the basic amplifier @ 200kHz reference      |    |

|      | signal                                                            | 51 |

| 2.38 | Simulated spectrum of the cascode amplifier @ 200kHz reference    |    |

|      | signal                                                            | 51 |

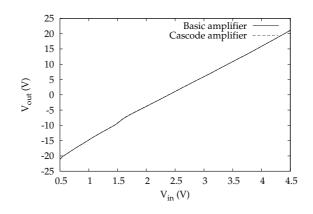

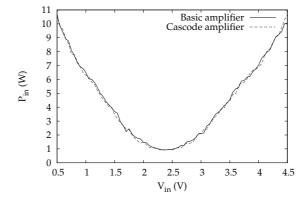

| 2.39 | Simulated linearity of both amplifiers                            | 53 |

| 2.40 | Simulated input power of both amplifiers                          | 54 |

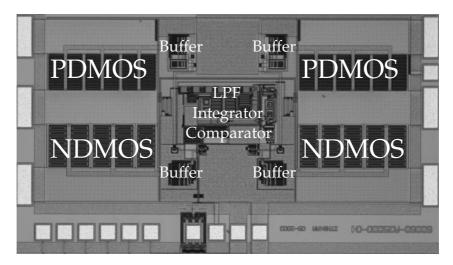

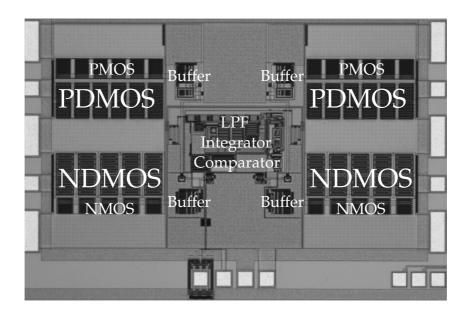

| 2.41 | Die photograph of the amplifier processed, basic output stage     | 55 |

| 2.42 | Die photograph of the amplifier processed, cascode output stage   | 56 |

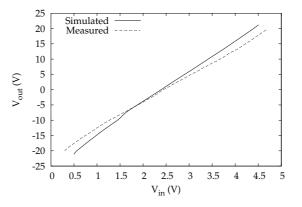

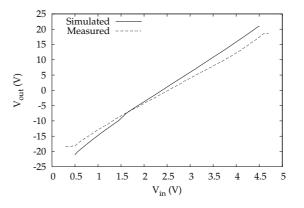

| 2.43 | Simulated and measured linearity of the basic amplifier           | 57 |

| 2.44 | Simulated and measured linearity of the cascode amplifier         | 57 |

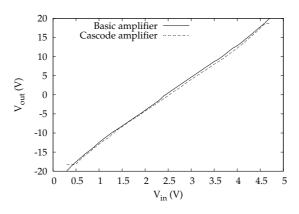

| 2.45 | Measured linearity of both amplifiers                             | 58 |

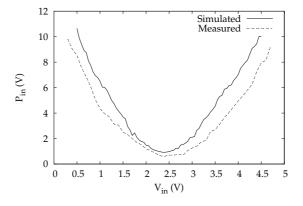

| 2.46 | Simulated and measured input power of the basic amplifier         | 59 |

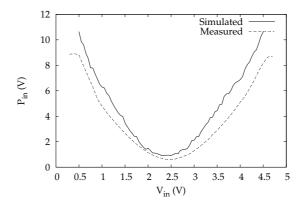

| 2.47 | Simulated and measured input power of the cascode amplifier       | 59 |

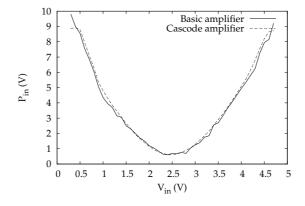

| 2.48 | Measured input power of both amplifiers                           | 60 |

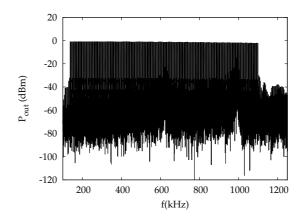

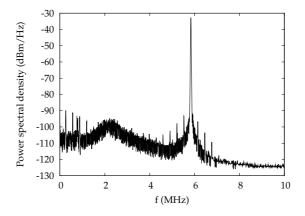

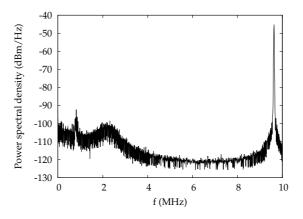

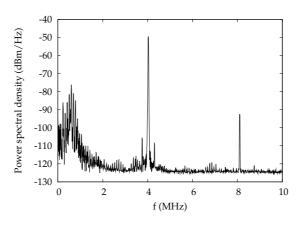

| 2.49 | Full-rate ADSL output spectrum                                    | 60 |

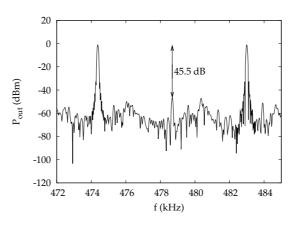

| 2.50 | Detail of the MTPR output spectrum                                | 61 |

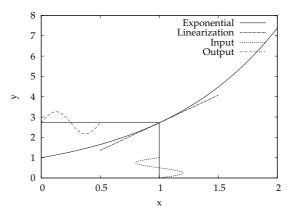

| 3.1  | Exponential transfer function with small signal parameters        | 66 |

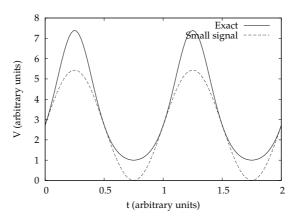

| 3.2  | Exact and small signal output response                            | 67 |

| 3.3  | Block diagram of non-linearity and approximation                  | 68 |

X

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

| 3.4  |                                                                                      | 72  |

|------|--------------------------------------------------------------------------------------|-----|

| 3.5  |                                                                                      | 75  |

| 3.6  |                                                                                      | 76  |

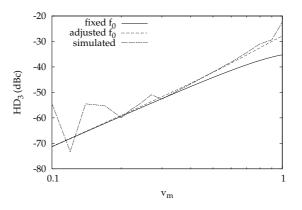

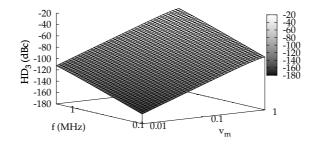

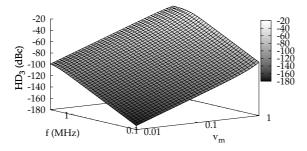

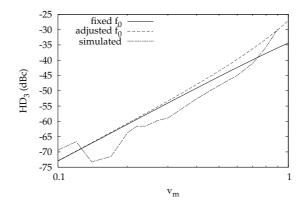

| 3.7  |                                                                                      | 84  |

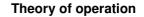

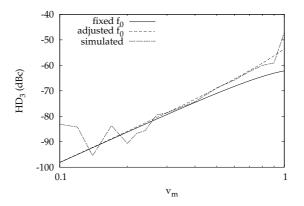

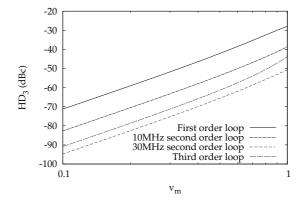

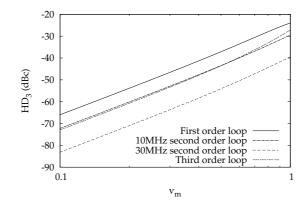

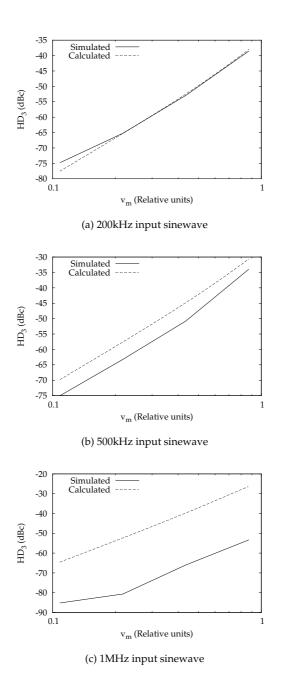

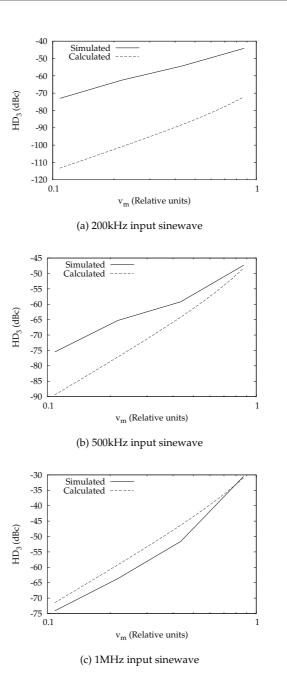

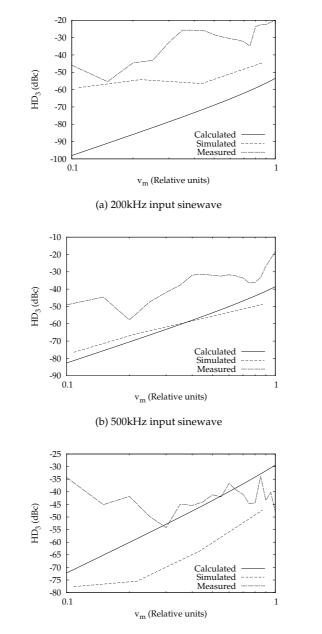

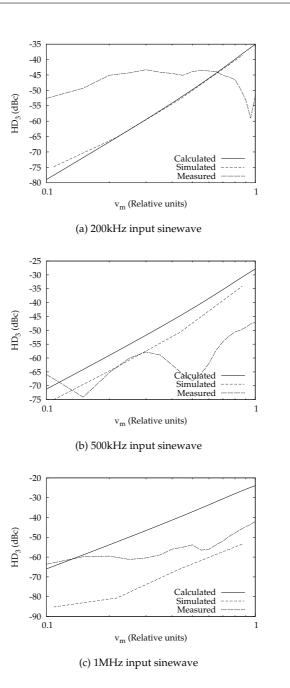

| 3.8  | HD <sub>3</sub> as function of $v_m$ and $f$ , 6MHz first order loop, $v_m$ compen-  |     |

|      |                                                                                      | 84  |

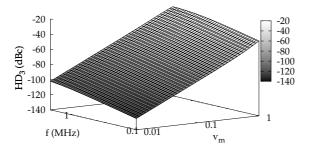

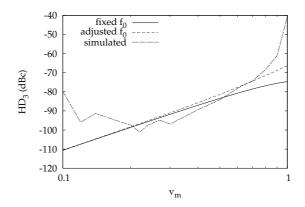

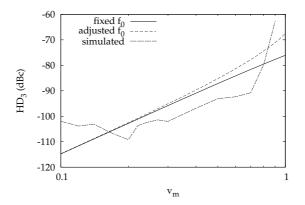

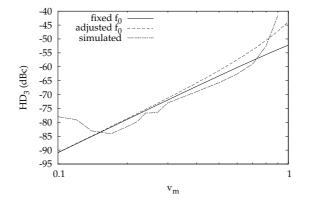

| 3.9  | Comparison of calculated and simulated HD <sub>3</sub> , first order loop,           |     |

|      | 200kHz signal                                                                        | 85  |

| 3.10 | Comparison of calculated and simulated HD <sub>3</sub> , first order loop,           |     |

|      | •                                                                                    | 85  |

| 3.11 | Comparison of calculated and simulated HD <sub>3</sub> , first order loop,           |     |

|      | •                                                                                    | 86  |

| 3.12 |                                                                                      | 88  |

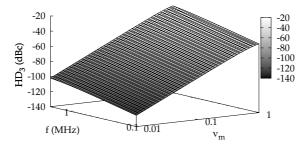

| 3.13 | HD <sub>3</sub> as function of $v_m$ and $f$ , 10MHz second order loop, ince $f_0$ . | 00  |

| 0.10 |                                                                                      | 89  |

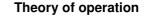

| 3.14 | Comparison of calculated and simulated HD <sub>3</sub> , 10MHz second                | 0)  |

| 5.14 |                                                                                      | 00  |

| 0.15 |                                                                                      | 89  |

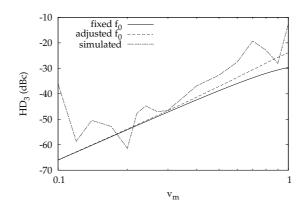

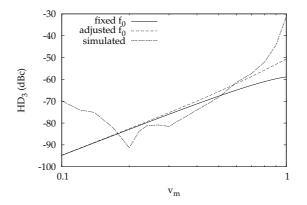

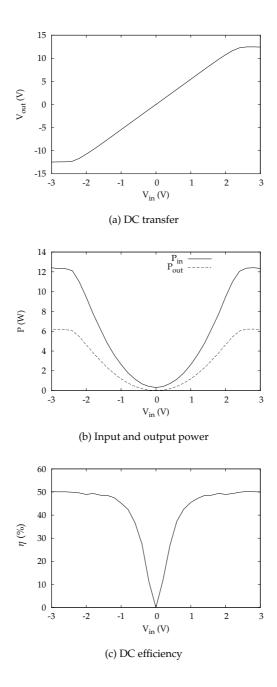

| 3.15 | Comparison of calculated and simulated HD <sub>3</sub> , 10MHz second                | ~ ~ |

|      | 1, 0                                                                                 | 90  |

| 3.16 | Comparison of calculated and simulated HD <sub>3</sub> , 10MHz second                |     |

|      | 1, 0                                                                                 | 90  |

| 3.17 | j, j                                             | 91  |

| 3.18 | HD <sub>3</sub> as function of $v_m$ and $f$ , 30MHz second order loop, $v_m$ com-   |     |

|      | pensated $f_0$                                                                       | 92  |

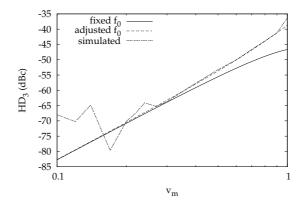

| 3.19 | Comparison of calculated and simulated HD <sub>3</sub> , 30MHz second                |     |

|      |                                                                                      | 92  |

| 3.20 | Comparison of calculated and simulated HD <sub>3</sub> , 30MHz second                |     |

| 0.20 |                                                                                      | 93  |

| 3.21 | Comparison of calculated and simulated $HD_3$ , 30MHz second                         |     |

| 0.21 | •                                                                                    | 93  |

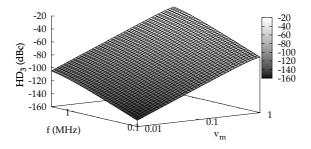

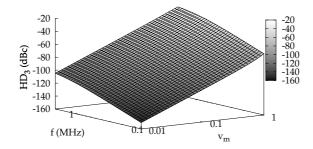

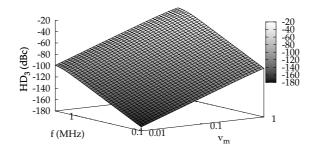

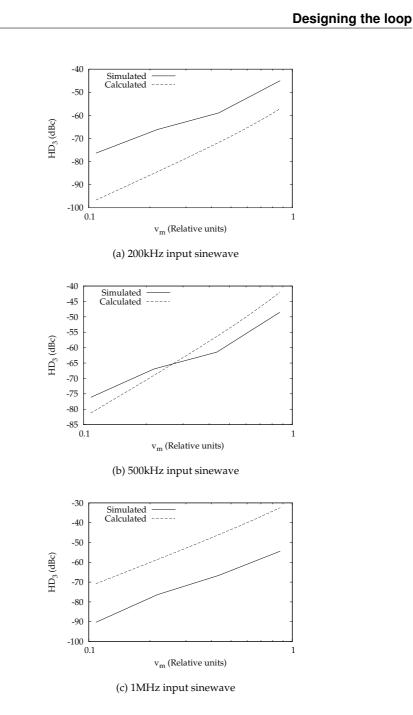

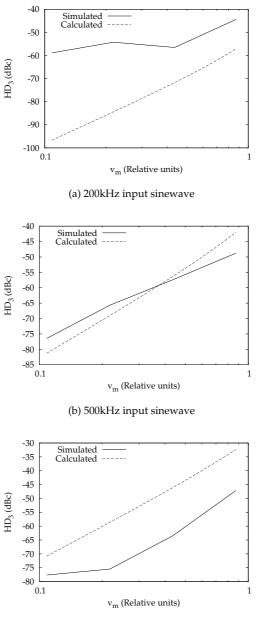

| 3.22 | 1 0                                                                                  | 95  |

| 3.23 | HD <sub>3</sub> as function of $v_m$ and $f$ , 10MHz third order loop, fixed $f_0$ . | /0  |

| 5.25 |                                                                                      | 96  |

| 2.24 | $\Gamma$                                                                             | 90  |

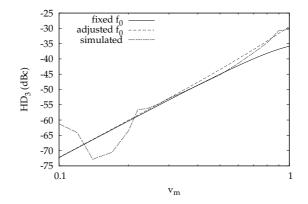

| 3.24 | Comparison of calculated and simulated HD <sub>3</sub> , third order loop,           | ~   |

|      |                                                                                      | 96  |

| 3.25 | Comparison of calculated and simulated HD <sub>3</sub> , third order loop,           |     |

|      | 0                                                                                    | 97  |

| 3.26 | Comparison of calculated and simulated HD <sub>3</sub> , third order loop,           |     |

|      | - 0                                                                                  | 97  |

| 3.27 |                                                                                      | 99  |

| 3.28 |                                                                                      | 99  |

| 3.29 |                                                                                      | 00  |

| 3.30 |                                                                                      | 00  |

#### xi

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

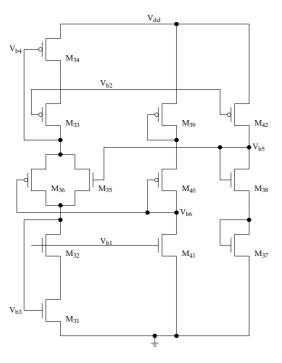

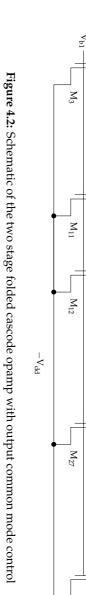

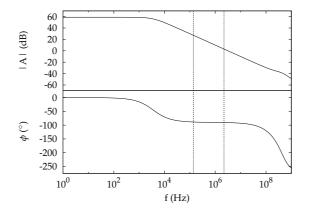

| 4.1 Basic schematic of a two stage folded cascode opamp           | 109     |

|-------------------------------------------------------------------|---------|

| 4.2 Schematic of the two stage folded cascode opamp with outp     |         |

| common mode control                                               |         |

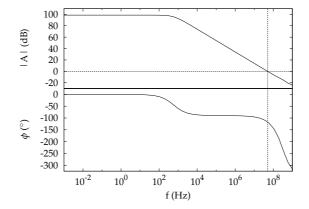

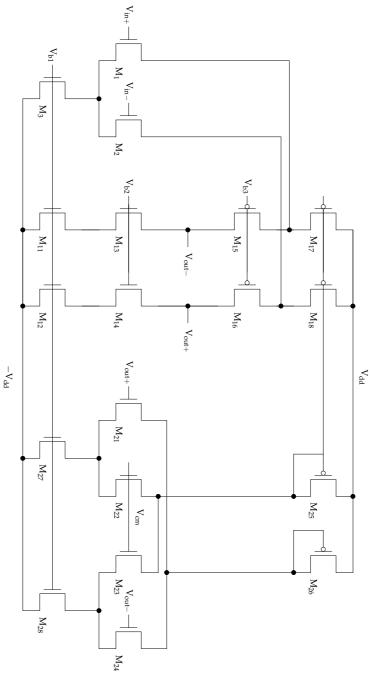

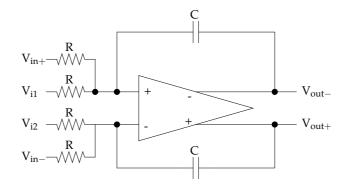

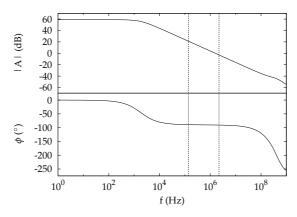

| 4.3 Simulated Bode diagram of the opamp                           | 113     |

| 4.4 Realized integrator                                           |         |

| 4.5 Bode plot of the 1.6MHz integrator                            | 114     |

| 4.6 Bode plot of the 3.2MHz integrator                            | 114     |

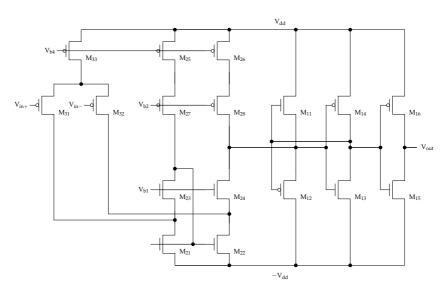

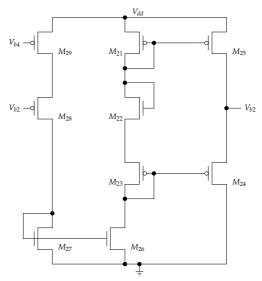

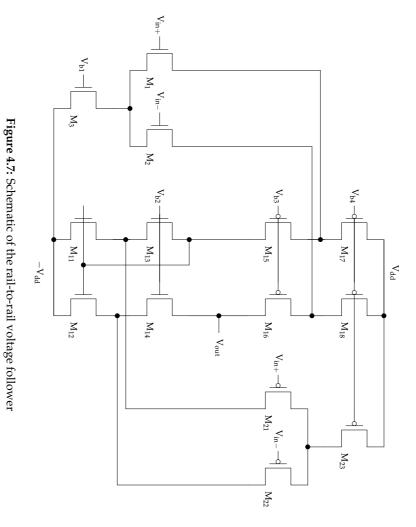

| 4.7 Schematic of the rail-to-rail voltage follower                | 116     |

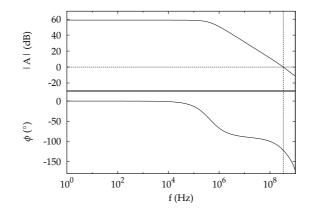

| 4.8 Bode diagram of the voltage follower, 1.65V input common m    | ode 117 |

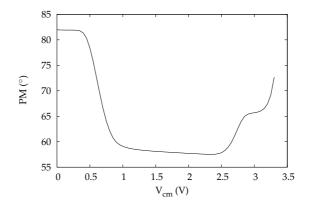

| 4.9 Phase margin of the opamp, depending on the common mo         | de      |

| input voltage                                                     | 117     |

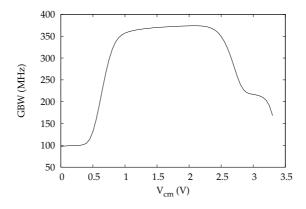

| 4.10 Gain bandwidth product of the opamp, depending on the co     | m-      |

| mon mode input voltage                                            |         |

| 4.11 Biasing circuit for the folded cascode stage                 | 119     |

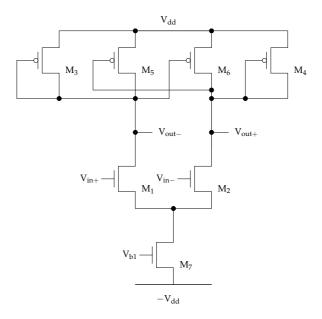

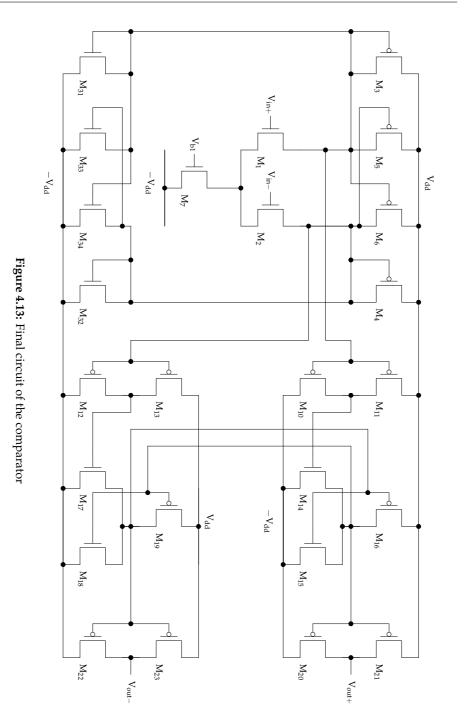

| 4.12 Basic circuit of the comparator                              |         |

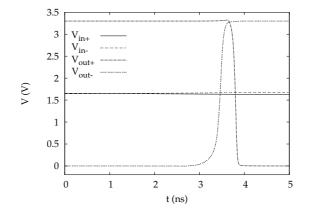

| 4.13 Final circuit of the comparator                              |         |

| 4.14 Simulation result of the comparator                          |         |

| 4.15 Schematic of the high voltage output stage                   |         |

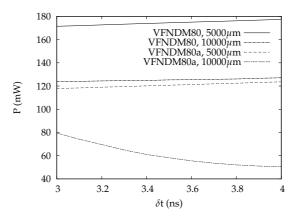

| 4.16 Comparison of power dissipation between the VFNDM80 a        | nd      |

| VFNDM80a DMOS as a function of the time delay, for different      |         |

| widths                                                            |         |

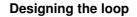

| 4.17 Output voltage as a function of duty cycle                   |         |

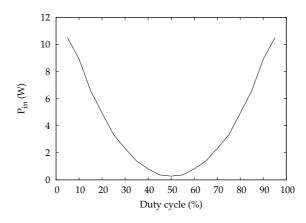

| 4.18 Input power as a function of duty cycle                      | 126     |

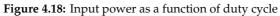

| 4.19 Schematic of the level shifter                               |         |

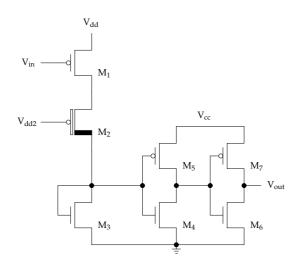

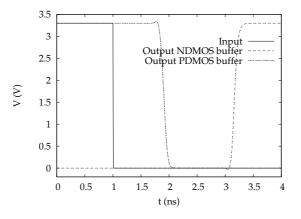

| 4.20 Schematic of the high to low level shifter                   |         |

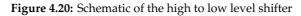

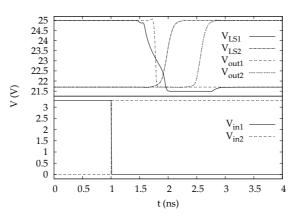

| 4.21 Simulation of the level shifter                              |         |

| 4.22 Simulation of the buffers                                    |         |

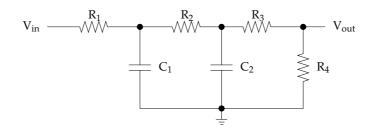

| 4.23 Schematic of the filter-divider                              |         |

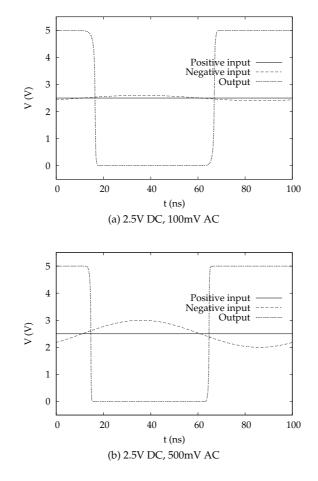

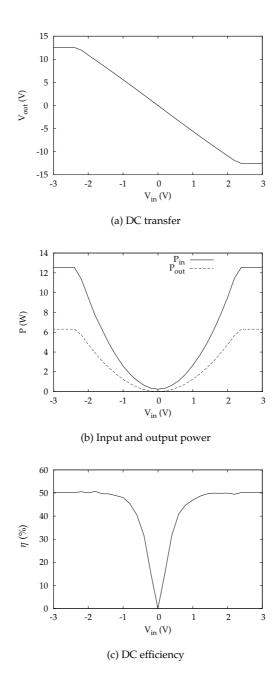

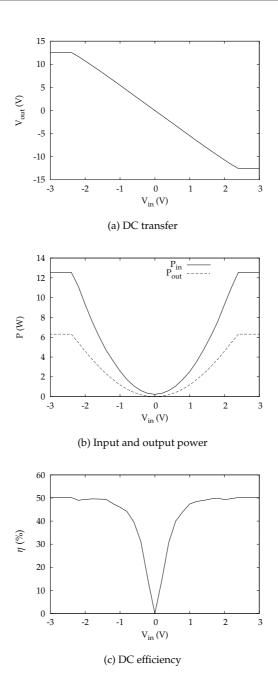

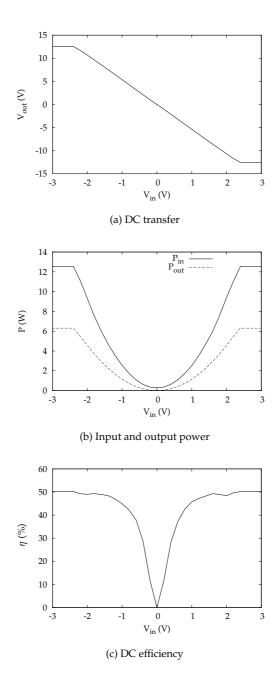

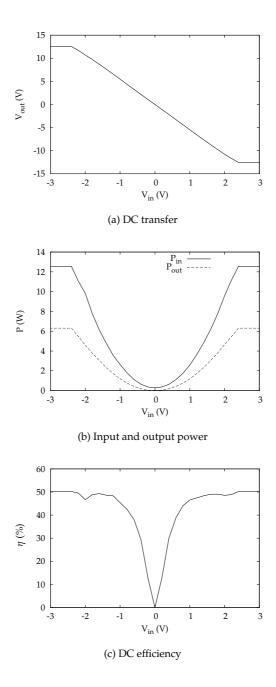

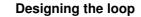

| 4.24 DC simulation of the first order system                      |         |

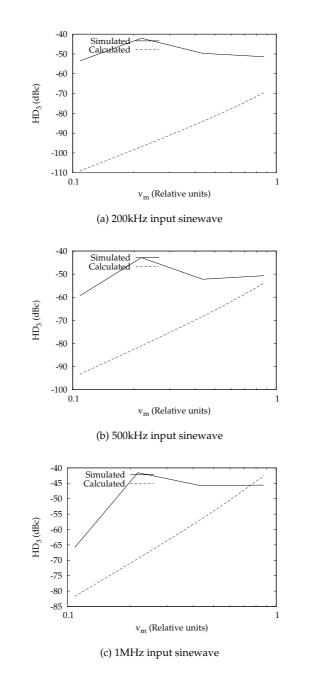

| 4.25 Third order harmonic distortion of the first order system    |         |

| 4.26 DC simulation of the 10MHz second order system               |         |

| 4.27 Third order harmonic distortion of the 10MHz second order sy |         |

| 4.28 DC simulation of the 30MHz second order system               |         |

| 4.29 Third order harmonic distortion of the 30MHz second order sy |         |

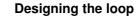

| 4.30 DC simulation of the third order system                      |         |

| 4.31 Third order harmonic distortion of the third order system    |         |

| 4.32 DC simulation of the second order system with independent l  |         |

| 4.33 Third order harmonic distortion of the second order system w |         |

| independent loops                                                 | 145     |

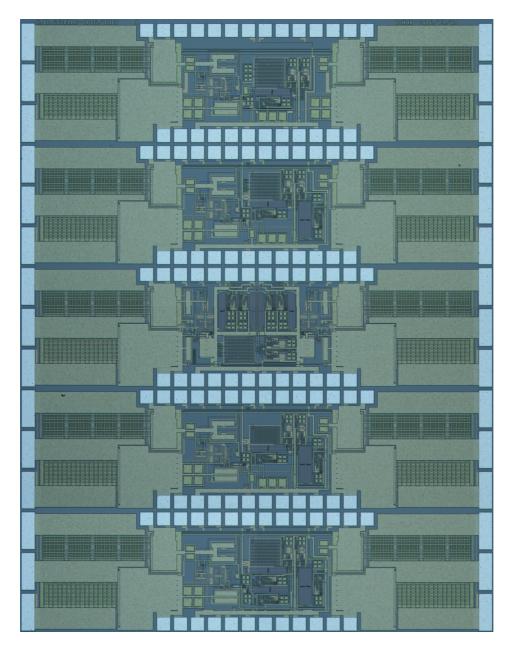

| 5.1 Die photograph of the amplifiers processed                    | 152     |

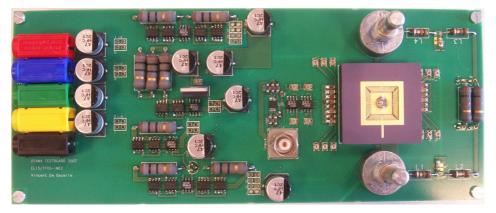

| 5.2 Photograph of the test board                                  | 153     |

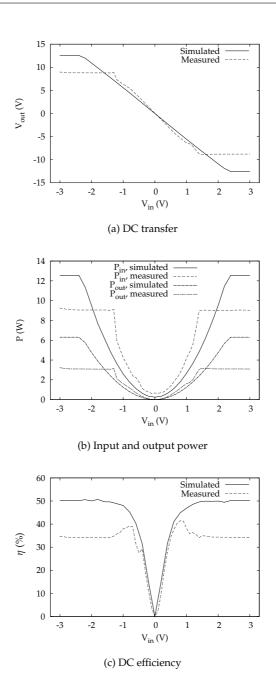

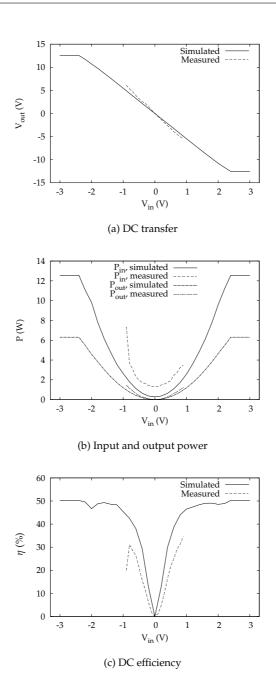

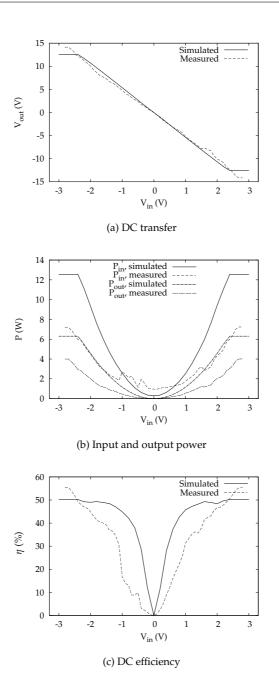

| 5.3 DC measurements on the first order system                     |         |

#### xii

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

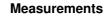

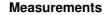

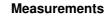

| 5.4  | Third order harmonic distortion of the first order system 156                 |

|------|-------------------------------------------------------------------------------|

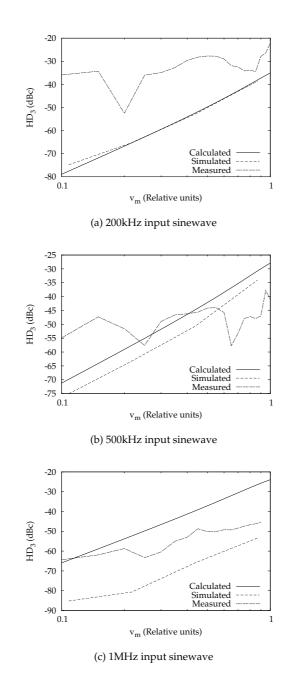

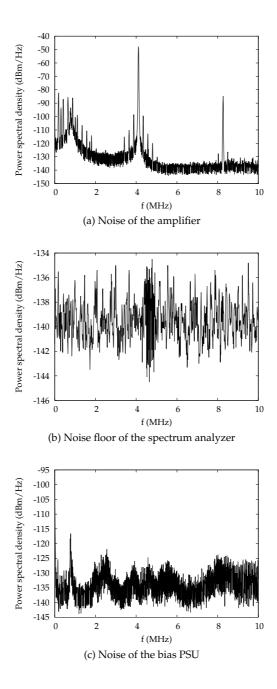

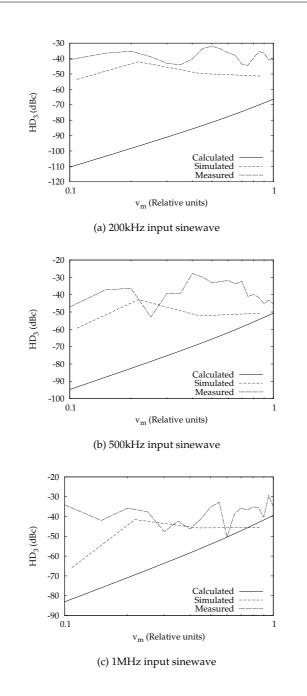

| 5.5  | Noise measurements on the first order system                                  |

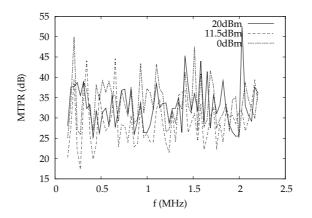

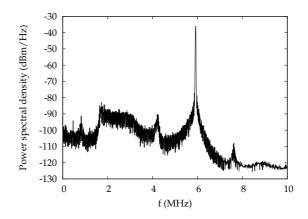

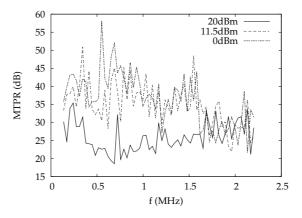

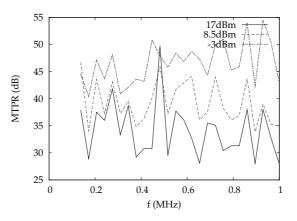

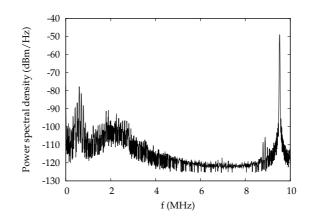

| 5.6  | MTPR measurements on the first order system                                   |

| 5.7  | DC measurements on the 10MHz second order system 160                          |

| 5.8  | Third order harmonic distortion of the 10MHz second order system161           |

| 5.9  | Noise measurement on the 10MHz second order system 162                        |

| 5.10 | MTPR measurements on the 10MHz second order system 162                        |

| 5.11 | DC measurements on the 30MHz second order system 163                          |

| 5.12 | Third order harmonic distortion of the 30MHz second order system165           |

| 5.13 | Noise measurement on the 30MHz second order system 166                        |

| 5.14 | MTPR measurements on the 30MHz second order system 166                        |

| 5.15 | DC measurements on the third order system                                     |

| 5.16 | Third order harmonic distortion of the third order system 168                 |

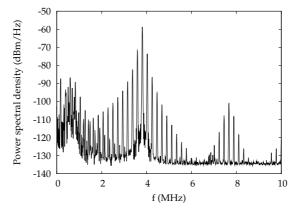

| 5.17 | Noise measurements on the third order system                                  |

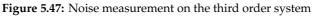

| 5.18 | MTPR measurements on the third order system                                   |

| 5.19 | DC measurements on the second order system with independent                   |

|      | loops                                                                         |

| 5.20 | Third order harmonic distortion of the second order system with               |

|      | independent loops                                                             |

| 5.21 | Noise measurement on the second order system with indepen-                    |

|      | dent loops                                                                    |

| 5.22 | MTPR measurements on the second order system with indepen-                    |

|      | dent loops                                                                    |

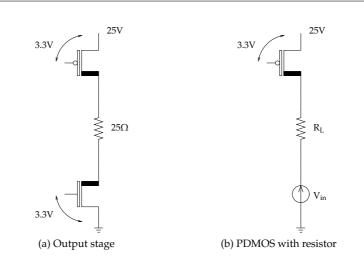

| 5.23 | Schematics for worst case simulations and PDMOS transistor mea-               |

|      | surements                                                                     |

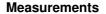

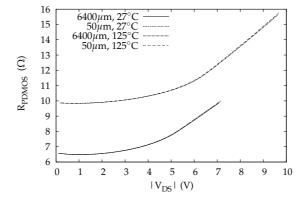

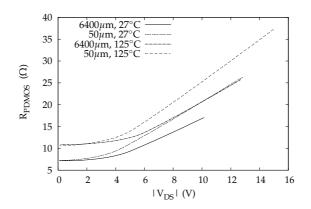

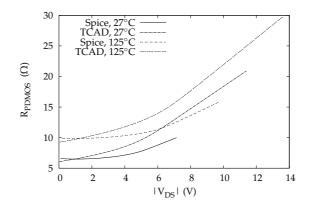

| 5.24 | Resistance of the PDMOS, spice simulation, typical                            |

| 5.25 | Resistance of the PDMOS, spice simulation, worst case 1 176                   |

| 5.26 | Resistance of the PDMOS, spice simulation, worst case 2 177                   |

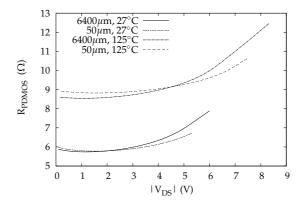

| 5.27 | Resistance of the PDMOS, comparison of spice and TCAD simu-                   |

|      | lations                                                                       |

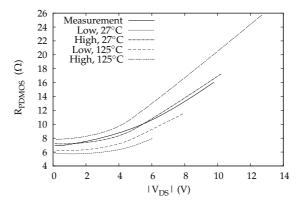

| 5.28 | Measured resistance of a $80\mu$ m PDMOS                                      |

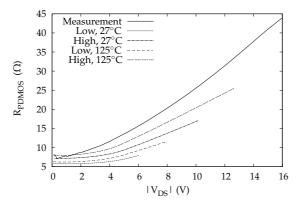

| 5.29 | Measured resistance of a $4818\mu$ m PDMOS                                    |

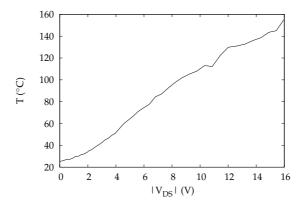

| 5.30 | Temperature of the $4818\mu$ m PDMOS package seal                             |

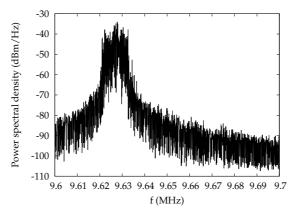

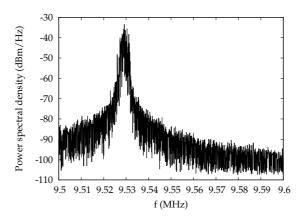

| 5.31 | Oscillating frequency detail, $25\Omega$ load, $30$ MHz second order loop 180 |

| 5.32 | Oscillating frequency detail, $50\Omega$ load, $30$ MHz second order loop 181 |

| 5.33 | DC measurements on the first order system                                     |

| 5.34 | Third order harmonic distortion of the first order system 183                 |

| 5.35 | Noise measurement on the first order system                                   |

| 5.36 | MTPR measurements on the first order system                                   |

| 5.37 | DC measurements on the 10MHz second order system 186                          |

| 5.38 | Third order harmonic distortion of the 10MHz second order system 187          |

| 5.39 | Noise measurement on the 10MHz second order system 188                        |

| 5.40 | MTPR measurements on the 10MHz second order system 188                        |

| 0.10 | with K measurements on the forming second order system 100                    |

## xiii

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

| 5.41 | DC measurements on the 30MHz second order system 189                |

|------|---------------------------------------------------------------------|

| 5.42 | Third order harmonic distortion of the 30MHz second order system190 |

| 5.43 | Noise measurement on the 30MHz second order system 191              |

| 5.44 | MTPR measurements on the 30MHz second order system 191              |

| 5.45 | DC measurements on the third order system 193                       |

| 5.46 | Third order harmonic distortion of the third order system 194       |

| 5.47 | Noise measurement on the third order system                         |

| 5.48 | MTPR measurements on the third order system 195                     |

| 5.49 | DC measurements on the second order system with independent         |

|      | loops                                                               |

| 5.50 | Third order harmonic distortion of the second order system with     |

|      | independent loops 197                                               |

| 5.51 | Noise measurement on the second order system with indepen-          |

|      | dent loops                                                          |

| 5.52 | MTPR measurements on the second order system with indepen-          |

|      | dent loops                                                          |

#### xiv

$\oplus$

$\oplus$

$\oplus$

## Samenvatting

Tijdens de laatste decennia zijn telecommunicatie in het algemeen en digitale datacommunicatie in het bijzonder een steeds belangrijkere rol gaan spelen in het dagdagelijkse leven. Terwijl de interconnectie van de grote datacenters gerealiseerd kan worden door relatief dure oplossingen zoals optische vezel en satellietverbindingen, omwille van het grote datadebiet dat daar verwerkt wordt, blijft het grote probleem het overbruggen van de laatste kilometers naar de eindgebruiker. Door gebruik te maken van het bestaande telefoon-, kabeltelevisie- of zelfs het elektriciteitsnetwerk kan deze kost echter beperkt worden.

Dit werk zal zich verder concentreren op de overdracht van digitale data over het twisted pair telefoonnetwerk, meer in het bijzonder met behulp van de familie van digital subscriber line (xDSL) technologieën. Waar xDSL gekend is omwille van zijn hoge spectrale efficiëntie en immuniteit voor stoorinvloeden en vervorming, heeft deze het nadeel van een hoge crest factor, gedefinieerd als de verhouding van de piekwaarde tot de kwadratisch gemiddelde waarde van het signaal, en de nood aan sterk lineaire lijnversterkers, waardoor de gemiddelde vermogensefficiëntie beneden de 15% blijft. Dit houdt ook een beperking in van het aantal lijnen dat per wijkcentrale aangestuurd kan worden om te voldoen aan thermische- en vermogenseisen.

Een mogelijk alternatief om de efficiëntie op te drijven, is de klasse van nietlineaire versterkers, aangezien deze idealiter een efficiëntie van 100% hebben. Dit betekent natuurlijk ook dat een zorgvuldig ontwerp nodig is om aan de lineariteitseisen te voldoen.

Het soort versterker dat verder doorheen dit boek gebruikt zal worden, is een asynchrone versie van de klassieke pulswijdte modulator (PWM). In plaats van het ingangssignaal te vergelijken met een zaagtand referentiesignaal op vaste frequentie, wordt een laagdoorlaat gefilterde versie van de blokgolfuitgang gebruikt. Het eindresultaat is dus een oscillator, door het gebruik van positieve terugkoppeling in de lus, met het efficiëntievoordeel van PWM, maar waarbij het in principe mogelijk moet zijn om op lagere schakelfrequenties te werken, wat natuurlijk de schakelverliezen vermindert. Analoog aan de naamgeving bij synchrone  $\Sigma\Delta$  omvormers, die een gelijkaardig blokschema hebben, wordt de "orde" van de versterker bepaald door het aantal invertoren in het voorwaartse signaalpad om systematische identificatie van het blokdiagram te vereenvoudigen.

Het werkingsprincipe van deze asynchrone lijnversterker wordt getest in hoofdstuk 2 door de implementatie van een nulde en een eerste orde versterker in de AMIS  $0.7\mu$ m I<sup>2</sup>T100 100V technologie, die werkt op een voedingsspanning van 50V.

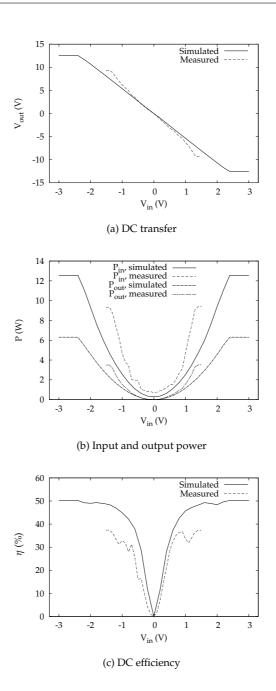

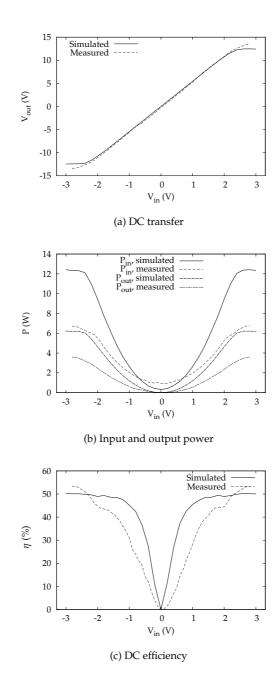

Het ongebalanceerde nulde orde systeem blijkt op een lagere oscillatiefrequentie te werken dan gesimuleerd door de toevoeging van verschillende meetpaden, met een hogere efficiëntie en distorsie tot gevolg. Voor een 200kHz, 10V referentie uitgangssignaal resulteert dit in een gesimuleerde distorsie van 6.07% en 27.91% efficiëntie en de gemeten waarden 7.49% voor de distorsie met 31% efficiëntie.

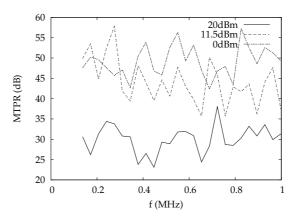

Het differentiële eerste orde systeem werkt ook op een lagere oscillatiefrequentie door onvoldoend gemodelleerde component parasitairen en extra parasitairen in de lay-out, wat opnieuw een positieve invloed heeft op de efficiëntie. De gemeten efficiëntie voor een typisch ADSL signaal is ongeveer 13% tegenover een 10% schatting gebaseerd op simulaties. Voor de eerste orde lus is de lineariteit bepaald door de multitone power ratio (MTPR) op te meten, aangezien het uiteindelijk deze waarde is die in de specificaties opgenomen is. Hiertoe wordt een DSL signaal versterkt, waarbij op sommige frequenties geen signaal uitgestuurd wordt. De MTPR is dan gedefinieerd als de verhouding van het vermogen, gemeten op de uitgestuurde frequenties, ten opzichte van het vermogen op deze ongebruikte frequenties. De gemeten waarde voor de MTPR is 40dB, wat hoger is dan de gesimuleerde 35dB, maar nog steeds te laag om te voldoen aan de vereiste voor ADSL lijnversterkers, die, afhankelijk van de bron, tussen 55dB en 65dB bedraagt.

Om het ontwerp van de lusorde en de filters van de asynchrone versterker op een systematischer manier aan te pakken, is een meer wiskundige beschrijving van het systeemgedrag vereist. Alhoewel er legio manieren zijn om het gedrag van lineaire systemen te beschrijven en het gedrag van PWM versterkers vereenvoudigd wordt door het gebruik van een synchrone klok, zijn deze methodes niet onmiddellijk toepasbaar op de asynchrone versterker.

De berekening van de oscillatiefrequentie is gebaseerd op een lineaire benadering van de niet-lineaire component in de lus, door gebruik te maken van de beschrijvendefunctietheorie en het Nyquist criterium voor stabiliteit van systemen in gesloten lus. De schatting van de derde orde harmonische component van zijn kant gebeurt door het verwachte uitgangssignaal gedurende een oscillatieperiode uit te schrijven als een Fourier reeks en die dan uit te breiden tot een volledige signaalperiode.

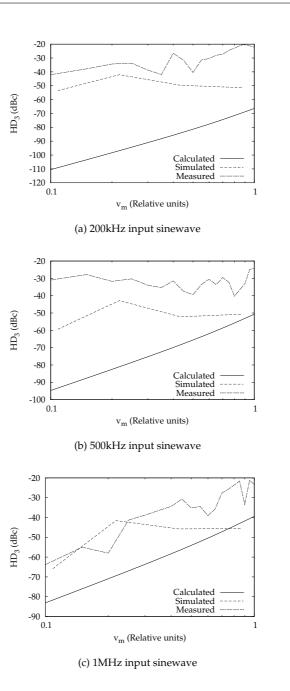

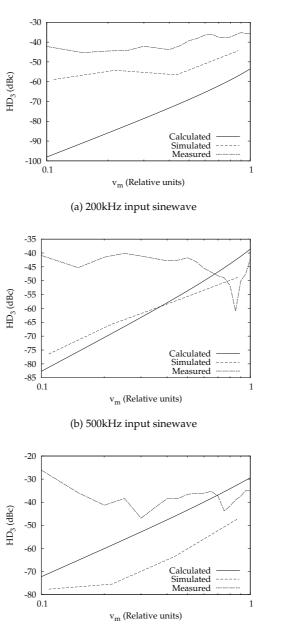

Dit leidt uiteindelijk tot een stel vergelijkingen die afhankelijk zijn van alle tijdconstanten van het systeem. Deze berekeningen zijn uitgevoerd in hoofdstuk 3, waar de systeemparameters van een eerste en derde orde lus zijn bepaald, samen met deze van een tweede orde lus met hoge en een met een lagere oscillatiefrequentie.

xvi

De simulatieresultaten van de systemen met de berekende parameters komen goed overeen met de berekende voorspellingen en leiden tot het niet zo verrassende besluit dat een hogere lusorde of oscillatiefrequentie beiden een lagere distorsie en hogere MTPR waarde tot gevolg hebben.

De resultaten van deze berekeningen worden verder gebruikt als basis voor de simulaties in de AMIS  $0.35\mu$ m I<sup>3</sup>T80 80V technologie in hoofdstuk 4. In dit geval is de gekozen voedingsspanning 25V, wat een verdubbeling van de stroom tot gevolg heeft om nog steeds het vereiste vermogen te leveren aan de last.

Wegens de aanwezigheid van tijdvertragingen en parasitaire componenten in het circuit, moeten sommige tijdconstanten aangepast worden om de gewenste oscillatiefrequentie te behouden. Dit heeft natuurlijk tot gevolg dat de overeenkomst tussen de berekeningen van hoofdstuk 3 en de simulaties slechter zal worden naarmate de tijdvertraging toeneemt ten opzichte van de oscillatieperiode. Algemeen kan er besloten worden dat de simulaties behoorlijk goed overeenkomen met de berekeningen, rekening houdend met de ruwe benaderingen die bij de berekeningen gebruikt zijn.

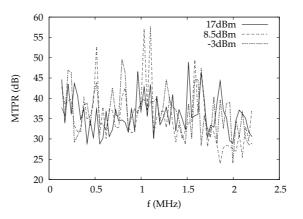

De simulatieresultaten van alle verschillende circuits leiden tot vergelijkbare schattingen voor de efficiëntie rond de 20%, wat duidelijk hoger is dan de voorgaande resultaten en de efficiënties die in de literatuur vermeld staan.

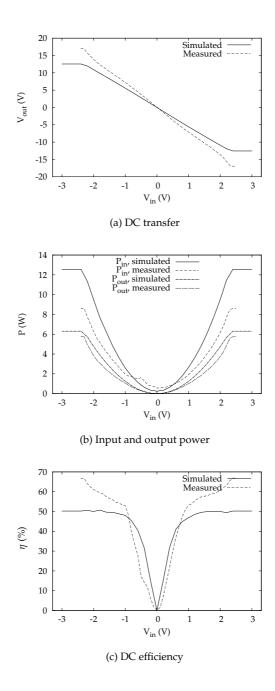

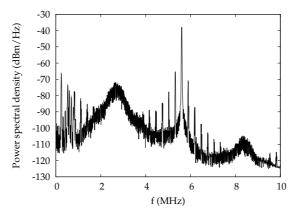

Tot slot wordt in hoofdstuk 5 een overzicht gegeven van alle meetresultaten op de geïntegreerde circuits. Het eerste wat waargenomen kan worden, is de vermindering in oscillatiefrequentie met ongeveer 30% bij alle circuits, wat in principe een negatieve invloed heeft op de lineariteit.

Ten tweede blijkt het vermogensverbruik in ongebruikte toestand merkbaar hoger te zijn dan gesimuleerd, wat tot gevolg heeft dat de efficiëntie gereduceerd wordt tot minder dan 13%. De oorzaak hiervan is van velerlei aard, zoals de invloed van parasitairen in de lay-out, het verschil in weglengte van de differentiële signaalpaden, de werktemperatuur en de variaties bij de productie. Daarenboven zal de lage waarde van de schakelvertraging van de uitgangstransistoren ook de aanvaardbare tolerantie verder verminderen, aangezien parasitaire tijdsvertragingen dan een relatief belangrijke invloed hebben op het schakeltijdstip en kortsluitstromen in de uitgangstrap mogelijk zijn.

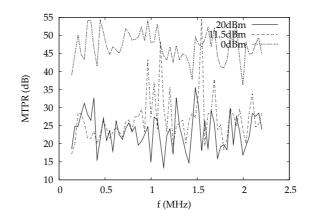

De gemeten waarde voor de MTPR is beperkt tot 20 à 30dB, wat duidelijk minder is dan de gesimuleerde waarden. Het sterk verminderde bereik van de uitgangsspanning, ongeveer 9V in plaats van de gesimuleerde minimale waarde van 12.5V, vormt een belangrijke indicatie met betrekking tot de oorzaak van dit probleem. Uiteindelijk blijkt de zelfopwarming van de uitgangstransistoren, ten minste gedeeltelijk, verantwoordelijk te zijn voor dit verschil, omdat een gedeelte van de terminatieweerstand voor het filter in de uitgangstrap geïntegreerd is in de transistoren om op silicium oppervlakte te kunnen besparen. Bijkomende oorzaken voor de lagere lineariteit kunnen de niet-lineariteit van de geïntegreerde

$\oplus$

passieve componenten en de opamps zijn, wat niet verder geverifieerd kon worden, aangezien deze signalen niet geconnecteerd zijn met een meetpad.

Verdere simulaties op de circuits, met toevoeging van bijkomende weerstand in serie met de uitgangstransistoren, vertonen een gelijkaardig gedrag als de metingen en wijzen op een toename van de derde orde harmonische met ongeveer 20dB. Bijkomende metingen, met verhoogde lastweerstand om de relatieve invloed van de impedantie van de uitgangstransistoren te beperken, leiden reeds tot een toename van de MTPR van ongeveer 10dB, wat de invloed van zelfopwarming op de performantie van de versterker bevestigt.

#### xviii

Æ

$\oplus$

Œ

## Summary

During the last decades, telecommunication in general and digital data communication in particular played an increasingly prominent role in everyday life. While the interconnection of large data centres, based on their data flow, can be obtained by rather expensive solutions such as optical fibre and satellite communication the main problem remains bridging "the last mile" to the end user. However, the use of pre-existing infrastructure, such as the telephone and cable TV network or even the power grid, can alleviate this cost.

This work will further focus on the transmission of digital data over the twisted pair telephone network, more specifically on the digital subscriber line (xDSL) technology family. While xDSL is known to be highly spectral efficient and immune to distortion, it has the disadvantage of a high crest factor, defined as the peak to root mean square ratio of the signal, and to require highly linear line drivers, resulting in power efficiencies well below 15%. This limits the number of lines that can be served at the central office, due to thermal and power requirements.

A possible alternative to increase the efficiency would be to use non-linear amplifiers, based on their ideal efficiency of 100%. As a consequence, special care must be taken in order to obtain the linearity required.

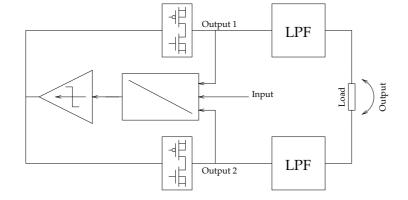

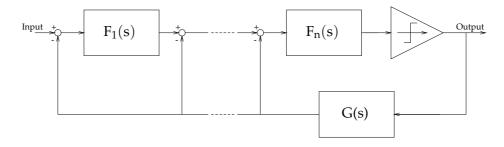

The amplifier class implemented in this work is an asynchronous version of the classical pulse width modulated (PWM) amplifier. Instead of comparing the input signal with a sawtooth reference signal at fixed frequency, a low pass filtered version of the square wave output is used. The final result basically is an oscillator, due to positive feedback in the loop, having the efficiency advantage of PWM circuits, but supposedly at lower switching frequencies, thus reducing switching losses. In analogy with the nomenclature used with synchronous  $\Sigma\Delta$  converters, which also have a similar block diagram, the "order" of the amplifier is determined by the number of integrators in the forward signal path, to simplify systematic identification of the block diagram.

The basic concept of the asynchronous line driver is verified in chapter 2 by the implementation of a zeroth and first order amplifier in the AMIS  $0.7\mu$ m I<sup>2</sup>T100 100V technology, operating at a 50V supply voltage.

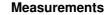

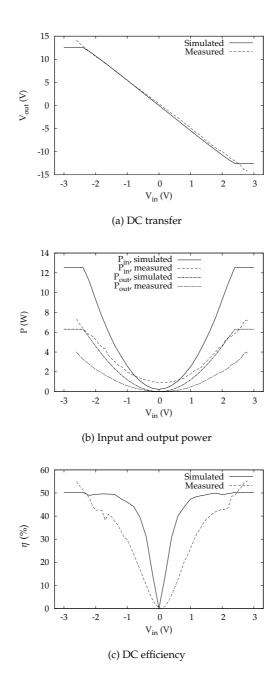

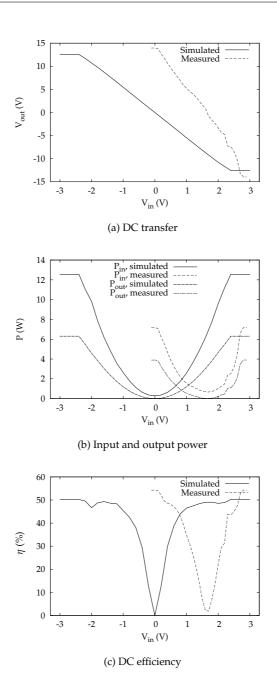

The single ended zeroth order system was verified to operate at a slightly re-

duced oscillating frequency as compared to the simulations due to the insertion of several measurement pads, resulting in both higher efficiency and distortion. For the 200kHz, 10V reference output signal, this led to a simulated distortion of 6.07% at 27.91% efficiency and a measured 7.49% distortion at 31% efficiency.

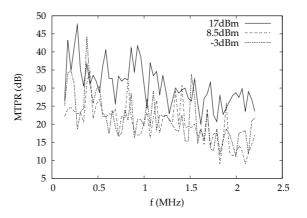

The balanced first order system also operates at a lower oscillating frequency due to insufficient component parasitics modelling and additional layout parasitics, which again has a positive influence on the amplifier efficiency. Using a typical ADSL signal, the measured efficiency is about 13% instead of the 10% estimate resulting from the simulations. For the first order loop, the multitone power ratio (MTPR) is used as the measure for linearity, since the DSL specifications are based on this figure. For this test, a DSL like signal, composing of all but some DMT tones, is amplified by the line driver and the MTPR is determined as the difference between the nominal tone power and the power measured at the missing tone frequency. The measured 40dB MTPR also is slightly higher than the simulated 35dB, but this is still too low to fulfill the ADSL requirements, ranging from 55dB to 65dB depending on the source.

To allow for a more systematical design of loop order and the filters of the asynchronous amplifier, a mathematical description of the system behaviour is required. While there is a plethora of methods for describing linear circuits and the description of PWM amplifiers is simplified by the mere presence of a synchronous clock, these can not readily be applied on the asynchronous amplifier.

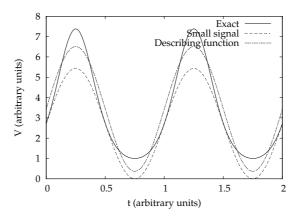

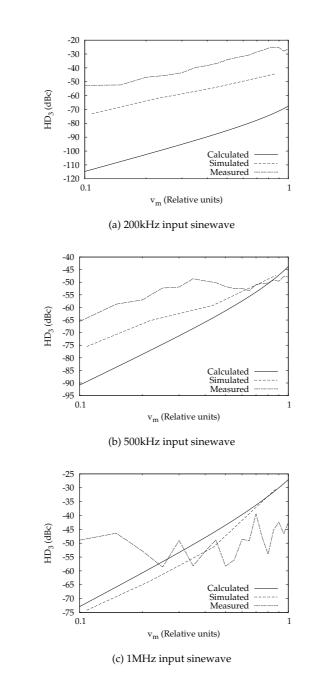

The calculation of the oscillating frequency is based on a linear approximation of the non-linear component in the loop, using the describing function theory and the Nyquist stability criterion for closed loop systems. The third order harmonic content on the other hand is approximated by writing the expected output signal during one oscillation period as its Fourier series, which can then be extended to the full input signal period.

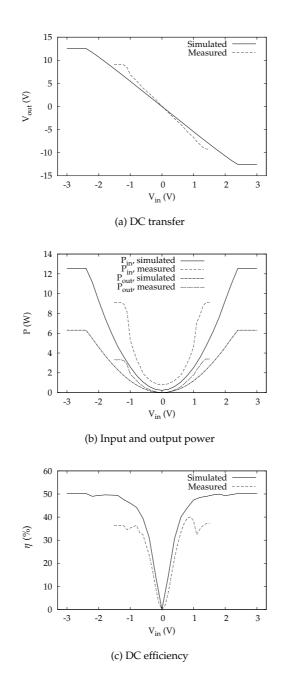

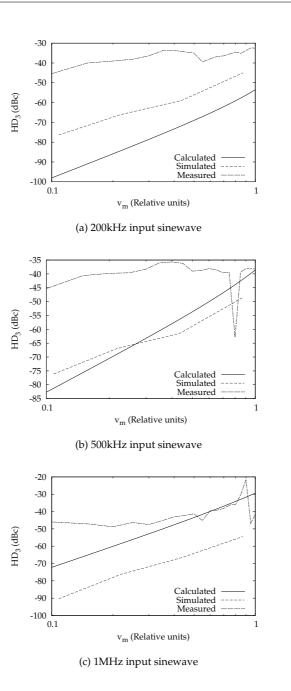

This finally leads to a set of equations, depending on all time constants of the system. These calculations are performed in chapter 3, where the system parameters of a first and third order loop are determined, in addition to two second order loops, one with a low and one with a high oscillating frequency.

The results of simulations using the parameters as calculated correspond well with the calculated predictions and lead to the not so surprising conclusion that an increase in loop order or oscillating frequency both lead to a lower distortion and increased MTPR figure.

The results from these calculations are then used as a basis for the simulations in chapter 4, using the AMIS  $0.35\mu$ m I<sup>3</sup>T80 80V technology. In this case, the supply voltage chosen is 25V, leading to a doubling of the current to deliver the required power to the load.

Due to the presence of time delays and parasitics in the circuit, some time constants needed adjustment in order to maintain the envisaged oscillating fre-

ΧХ

quency. As a consequence, the correspondence between the calculations from chapter 3 and the simulations will get worse with increasing time delay compared to the oscillating period. In general, it can be concluded that the system simulations still correspond rather well with the calculations, given the rough approximations made.

Simulations on all different circuits also lead to comparable efficiency figures of about 20%, which is significantly higher than the previous results and the efficiencies reported in the literature.

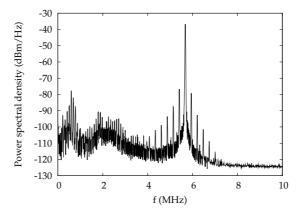

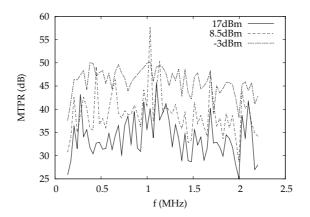

Chapter 5 finally gives an overview of all measurement results on the circuits implemented. A first observation is the reduction of the oscillating frequency by 30% for all circuits, which is expected to negatively impact the linearity.

Secondly, the idle power consumption of the amplifier is significantly higher than simulated, effectively limiting the estimated efficiency to under 13%. This is caused by a combination of several factors, such as layout parasitics, difference in length of the signal paths, operating temperature and process corners. In addition, the low value of the turn-on delay of the output transistors further reduces the acceptable tolerance, since additional time delays caused by parasitics will gain influence, possibly causing feed-through currents at the output stage.

The measured MTPR is limited to 20-30dB, well below the simulated values. An important indication as to which component might be the culprit, is the largely reduced output voltage swing, being about 9V instead of minimum 12.5V as simulated. As it turns out, self heating of the output transistors is, at least partially, to blame for this discrepancy, which is caused by the inclusion of part of the filter matching resistance in the output stage to reduce silicon area usage. Additional causes of distortion equally comprise the non-linearity of integrated passives and the opamp circuits, which could not be verified as those signals remain internal to the circuit.

Simulations on the circuits processed, including additional resistance in series with the output transistors, already exhibit similar behaviour as the measurements, suggesting a deterioration of the third order harmonic content by 20dB. Additional measurements with increased output impedance, to reduce the relative importance of the output transistor impedance on the system, lead to an increase of MTPR by about 10dB, which confirms the influence of self heating on the amplifier performance.

xxi

"doctoraat VDG" — 2009/8/13 — 11:30 — page xxii — #28

Summary

$\oplus$

$\oplus$

$\oplus$

$\oplus$

xxii

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

# **List of Abbreviations**

$\oplus$

$\oplus$

$\oplus$

⊕

| Notation | Meaning                                           |

|----------|---------------------------------------------------|

| ADC      | Analogue to Digital Converter                     |

| ADSL     | Asymmetric Digital Subscriber Line                |

| CF       | Crest Factor                                      |

| CMOS     | Complementary MOS                                 |

| CO       | Central Office                                    |

| DAC      | Digital to Analogue Converter                     |

| dBc      | Decibels relative to the carrier                  |

| DMOS     | Drain extended MOS                                |

| DMT      | Discrete Multitone                                |

| DSP      | Digital Signal Processor                          |

| GBW      | Gain Bandwidth Product                            |

| $HD_3$   | Third order Harmonic Distortion                   |

| IFFT     | Inverse Fast Fourier Transform                    |

| ISDN     | Integrated Services Digital Network               |

| LPF      | Low Pass Filter                                   |

| MOSFET   | Metal-Oxide-Semiconductor Field-Effect Transistor |

| MTPR     | Multitone Power Ratio                             |

| NDMOS    | N-type DMOS                                       |

| OFDM     | Orthogonal Frequency Division Multiplexing        |

| PDMOS    | P-type DMOS                                       |

| PM       | Phase Margin                                      |

| POTS     | Plain Old Telephone Service                       |

| PSU      | Power Supply Unit                                 |

| PWM      | Pulse Width Modulation                            |

| QAM      | Quadrature Amplitude Modulation                   |

| rms      | Root Mean Square                                  |

| TCAD     | Technology Computer-Aided Design                  |

| THD      | Total Harmonic Distortion                         |

| VDSL     | Very high speed Digital Subscriber Line           |

"doctoraat VDG" — 2009/8/13 — 11:30 — page xxiv — #30

$\bigoplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

Æ

## 1.1 Wire line communication

#### 1.1.1 Rise of the network

Since the invention of the electrical telegraph in the first half of the 19th century, private investors and government corporations start interconnecting these simple telecommunication devices. At first, wire length is rather limited, but at the beginning of the 20th century this network already interconnected major cities worldwide [1].

In parallel to these large scale interconnections, by the second half of the 19th century, the invention of the telephone caused a growing number of end users to show interest in the possibilities offered by this new technology. As with the telegraph, the first versions were standalone point to point connections using a single wire. Telegraph contractors however quickly realized they could extend the principle of the telegraph exchanges to this telephone, effectively creating a multi subscriber network. Since the bottleneck now shifted to the exchange operator, efforts were underway, first to simplify operation, but eventually to automate this process. Initially this also meant an increase in the number of wires needed — up to seven in the case of the Strowger automatic exchange [2]. Finally, only two wires were retained, this mainly for reasons of signal quality, leading to the classical twisted pair network.

#### **1.1.2** Extending the applications

As technology evolved in the 20th century, new applications emerged for the now full-grown telephone network. The increasing performance of computers, and the development of the ARPANET research network yielded expertise that was soon to be adopted in the analogue telephone networks [1]. At first, the end-to-end networks were digitized, increasing capacity and data quality. Later on, modems were used to allow for communication between computers, and the integrated services digital network (ISDN, originally Integriertes Sprach- und Datennetz) enabled a fully digitized path between end users. A further improvement of this digital communication is the xDSL family, of which asymmetric digital subscriber line (ADSL) and very high speed digital subscriber line (VDSL) are the best known members. A key difference between the classical modem and xDSL is the fact that xDSL uses its own frequency band, allowing for simultaneous use of telephone and xDSL communication.

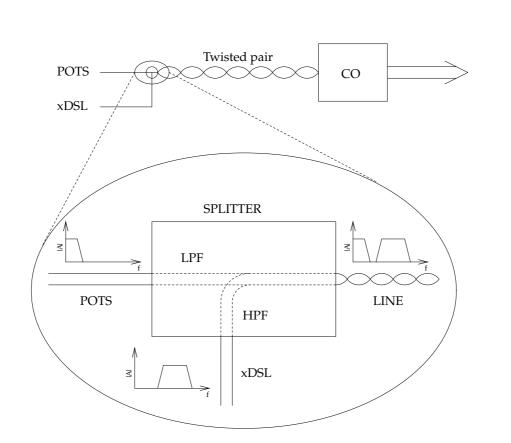

A simplified diagram of the combination of plain old telephone service (POTS) and xDSL between end user and central office (CO) is given in Fig. 1.1.

#### **1.1.3** Some properties of xDSL

The main advantage of xDSL over alternative forms of networking, such as optical fibre, is the use of the existing telephone wires, so the investments required usually are limited. However, the bandwidth of the wire pair will limit the bit rate and wire length. While this could be solved by increasing the power transmitted, cross-talk at both the transmitter and receiver end will further limit the quality of the signal, effectively putting an upper limit of about 5km on the wire length [3][4].

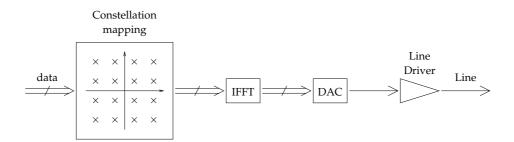

To reliably transmit the signal, xDSL uses a form of orthogonal frequency division multiplexing (OFDM) called discrete multitone (DMT), as depicted in Fig. 1.2. The digital data first is mapped onto the constellation of quadrature amplitude modulation (QAM), resulting in amplitude and phase information for each carrier frequency. This information then is transformed into analogue form for transmission by the use of an inverse fast Fourier transform (IFFT) and a digital to analogue converter (DAC) before being amplified by the line driver [5].

The result of this all is an encoding scheme, that can be implemented efficiently using a mainstream digital signal processor (DSP). The analogue output signal has a high spectral efficiency and low interference sensitivity. This explains the popularity of this modulation and its use in wireless networking, digital radio, digital TV etc.

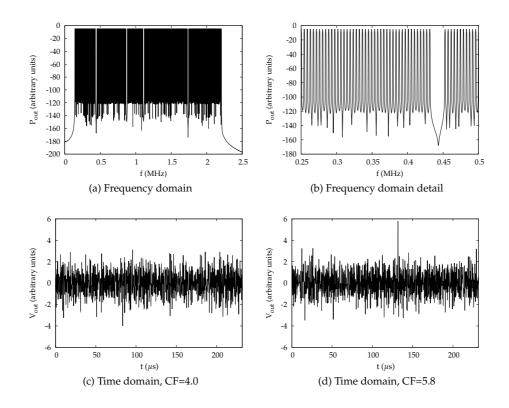

However, this digital efficiency is not entirely translated into the analogue domain. Although the signal has a clean frequency domain representation as shown in Fig. 1.3a, the time domain can exhibit a high crest factor (CF), defined as the

2

3

$\oplus$

$\oplus$

$\oplus$

#### 1.1 Wire line communication

$\oplus$

$\oplus$

$\oplus$

Figure 1.1: Simplified diagram of telephone interconnection

Figure 1.2: Principle of DMT encoding

$\oplus$

$\oplus$

peak to root mean square (rms) ratio of the signal. As a result, the analogue amplifier must be highly linear and might suffer low power efficiency [5][6]. Also note that all possible time domain representations will lead to Fig. 1.3a, regardless of CF, so Fig. 1.3c and Fig. 1.3d are only two possible results of the IFFT.

Figure 1.3: Frequency and time domain representation of a DMT encoded signal

## 1.2 Context and goal of this work

As already mentioned in Section 1.1.3, DMT suffers a high CF. To fulfill the high linearity demands, commercially available line drivers to date use some form of class AB amplifiers. However, using a CF of 5.8, the maximum achievable efficiency can be calculated as follows:

$$\eta = \frac{\pi}{4\text{CF}} = 13.5\%$$

Æ

$\oplus$

Œ

#### 1.2 Context and goal of this work

The result is a tremendous amount of power being dissipated at the CO, which limits the number of lines that can be served due to thermal and power requirements. As such, it might be interesting to investigate the applicability of less linear amplifiers. Although their frequency range is much lower, audio amplifiers form an excellent source of inspiration, because they have an even worse CF [7].

A first way to increase the efficiency, is to use a class G amplifier, as shown in Fig. 1.4 [8]. In this case, multiple supply voltages are fed into the amplifier, of which those yielding the highest efficiency are selected. An alternative is given in Fig. 1.5 [9], where the supply voltage is the output of a high efficiency switching amplifier, generating a voltage slightly higher than needed to ensure proper operation. In both cases this results in a higher average efficiency for the linear amplifiers.

Figure 1.4: Simplified diagram of a class G amplifier using multiple supply voltages

A different approach to the problem is to use highly efficient class D or pulse width modulation (PWM) amplifiers, as illustrated in Fig. 1.6. In its most simple form, the input signal is compared with a synchronous reference signal, often being a sawtooth. Depending on this comparison, the output will either be in the high or the low state. Since the output switches are ideally lossless, the efficiency of this amplifier is 100%. On the other hand, due to the hard non-linearity, the frequency of the synchronous reference signal must be sufficiently higher than the maximum input frequency to increase linearity.

Classical pulse width modulators (PWM) require a triangular or sawtooth reference input at a frequency of 10 to 100 times the highest signal frequency, which becomes impractical at xDSL frequencies. To lower the switching frequency while

5

⊕

"doctoraat VDG" - 2009/8/13 - 11:30 - page 6 - #36

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

Figure 1.6: Block diagram and corresponding waveforms of a basic PWM amplifier

#### 1.3 Outline

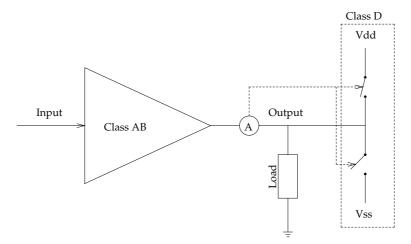

maintaining an acceptable level of distortion, a suitable feedback scheme has to be adopted, an example of which is given in Fig. 1.7 [10] for audio amplifiers. In this case, the main output power is delivered by a switching amplifier and switching is controlled by the error current delivered by a parallel class AB amplifier. When this current exceeds its threshold in any of both directions, the state of the class D output stage is changed accordingly. As a result, this amplifier is self-oscillating, at a frequency determined by the current threshold, with the output linearized by the class AB amplifier.

Figure 1.7: Example of an asynchronous mixed class AB and D amplifier

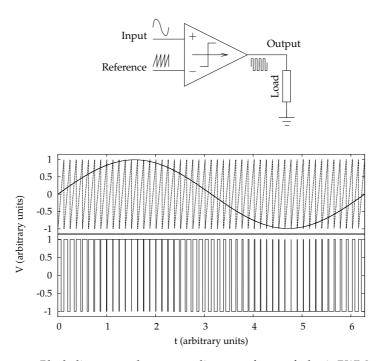

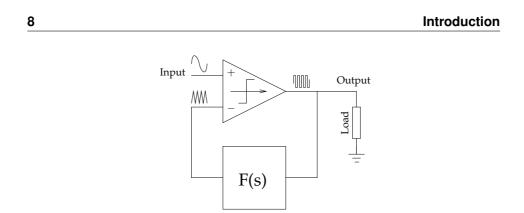

An alternative solution is to drop the external, synchronized reference input and use a filtered version of the output. By choosing an appropriate filter transfer function, the broad spectral content of the square wave output will be reduced, resulting in a more triangular signal that can be used as reference as depicted in Fig. 1.8 [11]. Basically, this amplifier is an oscillator, due to positive feedback, thus having the efficiency advantage of PWM circuits, but it should also be possible to achieve a comparable linearity at lower switching frequencies. On the other hand, the non-linearity and the asynchronous nature will complicate the mathematical description and performance prediction of the system.

# 1.3 Outline

$\oplus$

This work is further organized as follows. In chapter 2, the concept from Fig. 1.8 is further developed and simulated, finally resulting in the demonstration of the feasibility of the basic idea and the presentation of measurement results on a silicon integration of the circuits studied.

⊕

$\oplus$

$\oplus$

Æ

$\oplus$

$\oplus$

Figure 1.8: Block diagram of an asynchronous class D amplifier

Chapter 3 will then present a mathematical framework to predict the most important system parameters such as oscillating frequency and third order harmonic distortion. These calculations will result in values for the parameters of the building blocks, which will further be simulated on the transistor level in chapter 4. The measurements on the silicon implementations of these circuits and the corresponding remarks and conclusions are given in chapter 5. Finally, chapter 6 will give an overview of the most important conclusions of this work and possibilities for future research.

# References

- [1] Wikipedia. (2008, Jul.) Telegraphy. [Online]. Available: http://en.wikipedia. org/wiki/Telegraph

- [2] Wikipedia. (2008, Jul.) Telephone. [Online]. Available: http://en.wikipedia. org/wiki/Telephone

- [3] K. P. Ho, "Broadcast digital subscriber lines using discrete multitone for broadband access," *Microprocessors and Microsystems*, vol. 22, no. 10, pp. 605– 610, May 1999.

- [4] F. Sjöberg, M. Isaksson, R. Nilsson, P. Ödling, S. K. Wilson, and R. O. Börjesson, "Zipper: a duplex method for VDSL based on DMT," *IEEE Trans. Commun.*, vol. 47, no. 8, pp. 1245–1252, Aug. 1999.

- [5] D. J. G. Mestdagh, P. M. P. Spruyt, and B. Biran, "Effect of amplitude clipping in DMT-ADSL transceivers," *Electronics Letters*, vol. 29, no. 15, pp. 1354–1355, July 22 1993.

- [6] Wikipedia. (2008, Jul.) Orthogonal frequency-division multiplexing. [Online]. Available: http://en.wikipedia.org/wiki/Discrete\_multitone\_ modulation

- [7] Wikipedia. (2009, Jan.) Crest factor. [Online]. Available: http://en. wikipedia.org/wiki/Crest\_factor

- [8] F. H. Raab, "Average efficiency of class-G power amplifiers," IEEE Trans. Consum. Electron., vol. CE-32, no. 2, pp. 145–150, May 1986.

- [9] H. Nakagaki, N. Amada, and S. Inoue, "A high-efficiency audio power amplifier," *Journal of the Audio Engineering Society*, vol. 31, no. 6, pp. 430–436, Jun. 1983.

- [10] R. A. R. van der Zee and E. A. J. M. van Tuijl, "A power efficient audio amplifier combining switching and linear techniques," *IEEE J. Solid-State Circuits*, vol. 34, no. 7, pp. 985–991, Jul. 1999.

$\oplus$

$\oplus$

$\oplus$

$\oplus$

[11] J. Vanderkooy, "Comments on 'design parameters important for the optimization of very-high-fidelity PWM (class D) audio amplifiers'," *Journal of the Audio Engineering Society*, vol. 33, no. 10, pp. 809–811, Oct. 1985.

10

$\oplus$

$\oplus$

$\oplus$

This chapter describes the preliminary verification of the functioning of the asynchronous amplifier. The first section will give a brief overview of design choices to be made, in the second section a brief overview of the technology used is given, while the third and fourth section discuss simulations and measurement results of two silicon implementations.

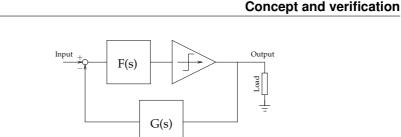

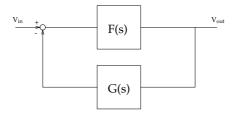

# 2.1 Preliminary considerations

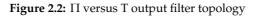

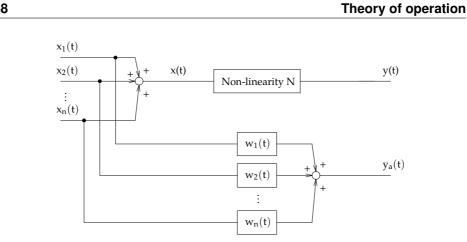

A slightly more generalized block diagram of the asynchronous line driver, as proposed in section 1.2, is shown in Fig. 2.1. The first choice to be made, is the transfer functions F(s) and G(s). For G(s), this choice is quite obvious, since the fed back signal should be a low pass filtered version of the square wave output, so a passive low pass filter (LPF) is sufficient. For F(s) however, there is a broad range of suitable candidates. Due to the resemblance between this circuit and  $\Sigma\Delta$  analogue to digital converters (ADC), two functions stand out: a simple LPF and an integrator. As such, also the naming convention from  $\Sigma\Delta$  ADC's can be used, describing the converter by the number of integrators in the forward path, which results in a zeroth or first order system for the circuit in Fig. 2.1.

A second design choice is the supply voltage required to deliver the output power specified. As explained in section 1.1.3, for DMT encoded signals, this requires knowledge of the nominal power corresponding to the rms value of the signal

Figure 2.1: Block diagram of an asynchronous class D amplifier

and the maximal CF. These values were found in [1] as 20dBm power with CF 6.8. Furthermore, the output power is delivered to the 100 $\Omega$  line impedance by means of a transformer. The winding ratio should be between 1:1 and 1:2 so as to not reduce the amplitude of the received signal excessively, since this is detected at resistors in series with the line driver output stage. For this first version, a winding ratio of 1:1 is chosen, thus the maximum output amplitude can be calculated as

$$V_{out} = \sqrt{P_{out}R CF} = 21.5V$$

(2.1)

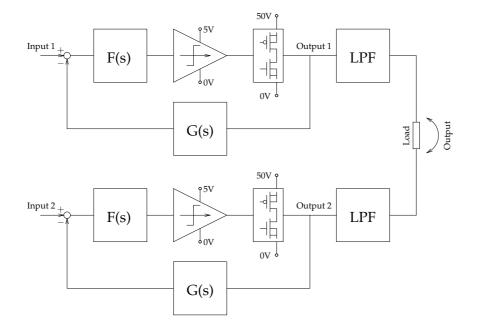

As such, the peak-to-peak voltage at the output is 43V.

For reasons of signal integrity, the output impedance of the amplifier should be matched, resulting in a doubling of the supply voltage required, but by opting for a bridge configuration, this can be halved again. To provide for some headroom, the supply voltage chosen is 50V. This also means that dedicated high voltage devices must be used. The technology chosen is the AMI Semiconductor I<sup>2</sup>T100  $0.7\mu$ m technology, offering such high voltage extensions up to 100V to a mainstream low voltage CMOS technology.

Additionally, the oscillating frequency must be chosen, taking into account the envisaged signal bandwidth. The circuits described in this chapter should be capable of handling signals in the range of 138kHz to 1.108MHz, corresponding to ADSL [1]. As such, designing for a switching frequency of approximately 10MHz seems a reasonable trade-off between output linearity and switching losses.

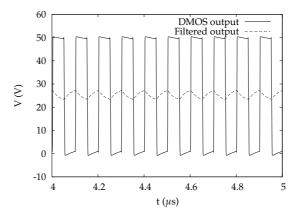

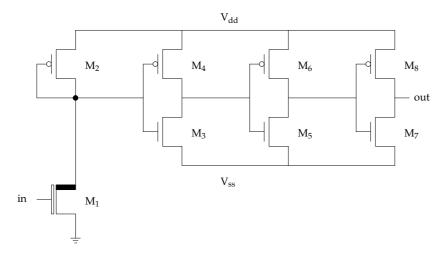

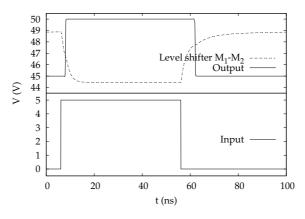

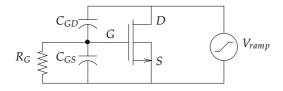

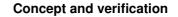

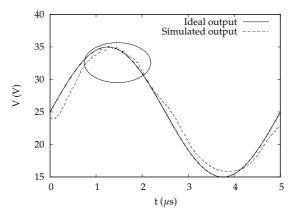

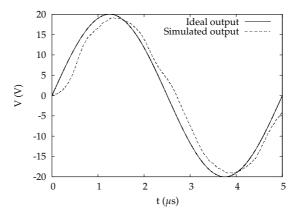

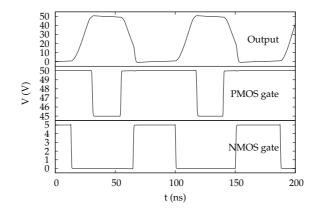

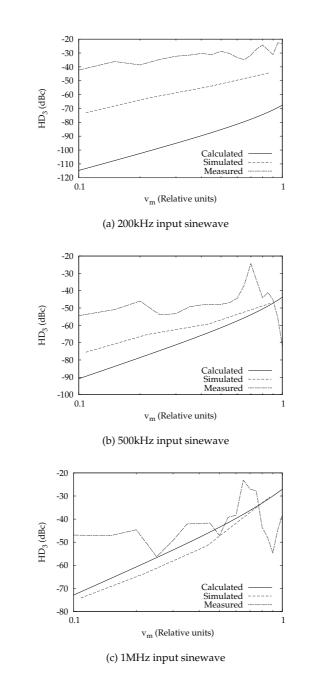

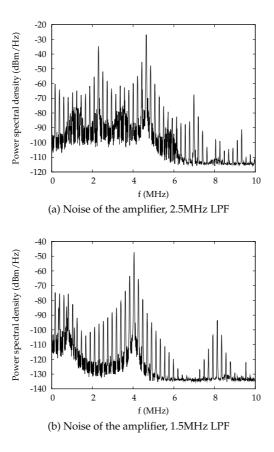

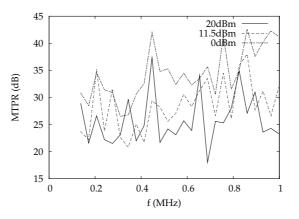

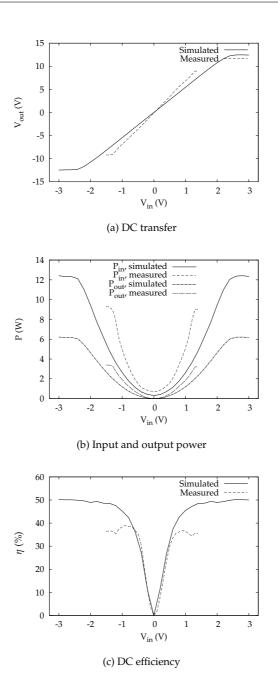

Finally, it should also be noted that the output delivers a lot of excess power to the load, due to the high spectral content of a square wave. To clean this up, a LPF is placed between the matching impedance and the load, allowing only the frequency band of interest to pass through and suppressing the square wave output. Of the two possible topologies, namely the  $\Pi$  and T networks as shown in Fig. 2.2, only the T network can be used, since the  $\Pi$  variant allows for high frequency current to be dissipated in the matching impedance, effectively decreasing efficiency.