Universiteit Gent Faculteit Toegepaste Wetenschappen Vakgroep Elektronica en Informatiesystemen

# Vermogenstransistoren in een Submicron Digitale CMOS-Technologie

Power Transistors in a Submicron Digital CMOS Technology

# Benoit Bakeroot

Proefschrift tot het verkrijgen van de graad van Doctor in de Toegepaste Wetenschappen Elektrotechniek Academiejaar 2003–2004

Promotoren: Prof. André Van Calster en Prof. Jan Doutreloigne

Universiteit Gent Vakgroep Elektronica en Informatiesystemen TFCG/IMEC Sint-Pietersnieuwstraat 41 B-9000 Gent België

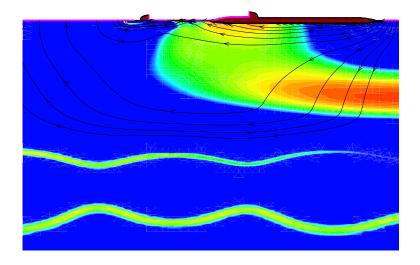

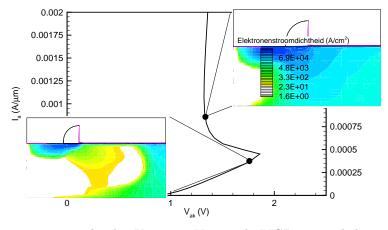

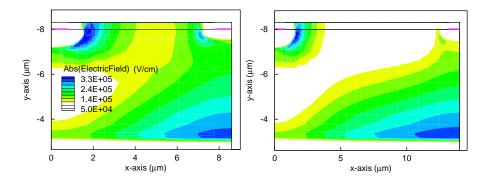

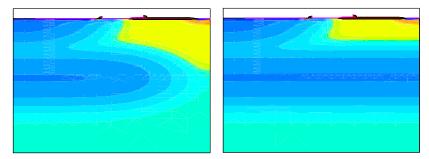

Picture on the front cover shows a lateral IGBT device with double buried layer structure (containing a patterned BLN) at on-state breakdown (red represents the highest electric fields). The black lines show how the hole current is flowing at that stage.

# Dankwoord

Dit manuscript mag dan wel door mezelf geschreven zijn, het zou niet tot stand gekomen zijn zonder de liefde en de steun van Vanessa, zonder de zorg van mijn ouders of zonder het vertrouwen van prof. Van Calster.

Het werk dat hier beschreven wordt, kon enkel verwezenlijkt worden met hulp van de eerste zorgen van Miguel, van het immer luisterend oor van prof. Jan Doutreloigne, van het wetenschappelijk aanstekelijk enthousiasme van Peter Moens. Dank aan AMIS en de technologiegroep van Marnix Tack voor het realiseren van de chips, in het bijzonder aan Davide Bolognesi en zijn (ex-)collega's Davy Villanueva, Dominique Wojciechowski en Henri-Xavier Delecourt. Ook Ronny Blomme, die steeds paraat stond bij het oplossen van de software- en hardwareproblemen, Peter Sebrechts voor de vele pc-hulp en de ganse TFCG-groep kon ik niet missen. Dank aan mijn lotgenoten uit Lausanne, Costin Anghel en Nasser Hefyene; aan Guido Groeseneken, Geert Van den Bosch en Brahim Elattari uit IMEC, Leuven voor de verhelderende discussies.

Niet in het minst zou ik mijn vrienden willen danken, vooral de eetmakkers die sinds het begin van mijn verblijf in de TFCG-groep elk middagmaal tot een rustpunt konden scheppen; Youri voor de vele levenswijsheden, Jürgen de oeverloze verteller; Michiel, Ewout, Piere en Johannes. Bedankt !

Benoit Bakeroot

Gent, 13 april 2004.

# ${\rm Inhoudsopgave}-{\rm Contents}$

| Neder | landst | calige Samenvatting (Dutch Summary)                                                         | 1  |

|-------|--------|---------------------------------------------------------------------------------------------|----|

| 1     | Inleid | ling                                                                                        | 1  |

|       |        | Een beetje geschiedenis                                                                     | 1  |

|       |        | Hoeveel vermogen? Welke technologie? Welke                                                  |    |

|       |        | bouwstenen?                                                                                 | 2  |

|       |        | Waarom TCAD?                                                                                | 4  |

|       |        | Doelstelling                                                                                | 5  |

|       |        | Overzicht                                                                                   | 5  |

| 2     | Fund   | amentele Beschouwingen                                                                      | 6  |

|       | 2.1    | Inleiding                                                                                   | 6  |

|       | 2.2    | De fysica                                                                                   | 7  |

|       | 2.3    | Wat is een vermogensbouwsteen ?                                                             | 8  |

|       | 2.4    | Gelijkrichters                                                                              | 8  |

|       |        | De ideale gelijkrichter                                                                     | 9  |

|       |        | De pn-diode                                                                                 | 9  |

|       |        | De PT-diode                                                                                 | 10 |

|       | 2.5    | Schakelaars                                                                                 | 11 |

|       |        | Stroomgecontroleerde schakelaars                                                            | 11 |

|       |        | Spanningsgecontroleerde schakelaars                                                         | 12 |

|       | 2.6    | Fundamentele concepten omtrent geïntegreerde ver-                                           |    |

|       |        | mogensschakelaars                                                                           | 12 |

|       |        | De siliciumlimiet $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                     | 12 |

|       |        | RESURF-effect                                                                               | 13 |

|       |        | PT- en RT-doorslag                                                                          | 13 |

|       |        | Tweede doorslag, terugslag en thermische instabi-                                           |    |

|       |        | liteit                                                                                      | 13 |

|       |        | Kirk-effect en adaptieve RESURF                                                             | 13 |

|       |        | SOA                                                                                         | 14 |

|       |        | Hoge injectie en geleidingsmodulatie                                                        | 15 |

|       |        | Isolatie                                                                                    | 15 |

| 3     | TCA    | D-Simulatie en -IJking                                                                      | 15 |

|       | 3.1    | Inleiding                                                                                   | 15 |

|       | 3.2    | Processimulatie en -ijking                                                                  | 15 |

|       |        | Het raster $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 15 |

|       |        | Simulatie en ijking                                                                         | 17 |

|       | 3.3    | Bouwsteensimulatie en -ijking                                                               | 18 |

|      |        | Van proces- naar transistorsimulatie              | 18 |

|------|--------|---------------------------------------------------|----|

|      |        | Transistorsimulatie en -ijking                    | 19 |

|      | 3.4    | Besluit                                           | 20 |

| 4    | Vermo  | gen-MOS                                           | 20 |

|      | 4.1    | Inleiding                                         | 20 |

|      | 4.2    | RESURF-effect                                     | 21 |

|      | 4.3    | De Siliciumlimiet                                 | 22 |

|      | 4.4    | Welke DMOS: n of p, lateraal of verticaal, RESURF |    |

|      |        | of niet ?                                         | 23 |

|      |        | N- of p-type ?                                    | 23 |

|      |        | Lateraal of verticaal ?                           | 24 |

|      |        | RESURF of niet ?                                  | 25 |

|      | 4.5    | Niet-zwevende, laterale, RESURF nDEMOS zon-       |    |

|      |        | der begraven lagen                                | 25 |

|      | 4.6    | Niet-zwevende, laterale RESURF nDEMOS op een      |    |

|      |        | p-type begraven laag                              | 26 |

|      | 4.7    | Zwevende, laterale, niet-RESURF nDEMOS op         |    |

|      |        | een n-type begraven laag                          | 27 |

|      | 4.8    | Zwevende, laterale, RESURF nDEMOS op twee         |    |

|      |        | begraven lagen                                    | 28 |

|      | 4.9    | Zwevende, geïntegreerde, verticale nDEMOS         | 29 |

|      | 4.10   | Zwevende, laterale RESURF pDEMOS                  | 30 |

|      |        | Waarom lateraal?                                  | 30 |

|      | 4.11   | Besluit                                           | 32 |

| 5    | IGBT   |                                                   | 33 |

|      | 5.1    | Inleiding                                         | 33 |

|      | 5.2    | Doorslag in een nLIGBT zonder begraven lagen      | 34 |

|      | 5.3    | Zwevende nLIGBT met BLN                           | 34 |

|      |        | Zwevende nLIGBT met BLN en een toegevoegde        |    |

|      |        | nbuffer                                           | 35 |

|      | 5.4    | Niet-zwevende nLIGBT met BLP                      | 37 |

|      | 5.5    | Zwevende nLIGBT met BLN en BLP                    | 38 |

|      | 5.6    | P-type LIGBTs                                     | 40 |

|      | 5.7    | Besluit                                           | 41 |

| 6    | Synops | sis                                               |    |

| Bibl |        |                                                   | 43 |

| Er       | Engelstalige tekst — Full version |        |                                                   |          |  |

|----------|-----------------------------------|--------|---------------------------------------------------|----------|--|

| 1        | Intr                              | oduct  |                                                   | 45       |  |

|          |                                   |        | History                                           | 45       |  |

|          |                                   |        | much power ? Which technology ? Which devices ? . | 46       |  |

|          |                                   |        | TCAD ?                                            | 48       |  |

|          |                                   |        | tive                                              | 49       |  |

|          |                                   | Outlir |                                                   | 50       |  |

|          |                                   | Refere | ences                                             | 50       |  |

| <b>2</b> | Fundamental Considerations        |        |                                                   |          |  |

|          | 2.1                               | Introd | luction                                           | 51       |  |

|          | 2.2                               | The P  | Physics                                           | 52       |  |

|          |                                   | 2.2.1  | Process, semiconductor and device physics         | 52       |  |

|          |                                   | 2.2.2  | General framework for device simulation           | 52       |  |

|          |                                   |        | Example: a silicon bar                            | 58       |  |

|          | 2.3                               | What   | is a power device ?                               | 61       |  |

|          | 2.4                               | Rectif |                                                   | 62       |  |

|          |                                   | 2.4.1  | The ideal rectifier                               | 62       |  |

|          |                                   | 2.4.2  | Junction diode                                    | 63       |  |

|          |                                   | 2.4.3  | Punch-through diode                               | 64       |  |

|          |                                   | 2.4.4  | P-i-N rectifier                                   | 65       |  |

|          |                                   | 2.4.5  | Other power rectifiers                            | 65       |  |

|          | 2.5                               | Switch | -                                                 | 66       |  |

|          |                                   | 2.5.1  | The ideal switch                                  | 66       |  |

|          |                                   | 2.5.2  | Current controlled switches                       | 66       |  |

|          |                                   | 2.0.2  | Power bipolar transistor                          | 66       |  |

|          |                                   |        | Power thyristors                                  | 67       |  |

|          |                                   | 2.5.3  | Voltage controlled switches                       | 68       |  |

|          |                                   | 2.0.0  | Power junction field-effect devices               | 68       |  |

|          |                                   |        | Power MOSFET                                      | 68       |  |

|          |                                   |        | Insulated gate bipolar transistor                 | 69       |  |

|          |                                   |        | MOS-controlled thyristors                         | 69       |  |

|          | 2.6                               | Funda  | amental Concepts Concerning                       | 03       |  |

|          | 2.0                               |        | atted Power Switches                              | 70       |  |

|          |                                   |        |                                                   |          |  |

|          |                                   | 2.6.1  | The silicon limit                                 | 70<br>70 |  |

|          |                                   | 2.6.2  | RESURF effect                                     | 70<br>71 |  |

|          |                                   | 2.6.3  | Punch-through and reach-through                   | 71       |  |

|          |                                   | 2.6.4  | Second breakdown, snapback and thermal runaway    |          |  |

|          |                                   | 2.6.5  | Kirk effect and adaptive RESURF                   | 72       |  |

|   |      | 2.6.6   | Safe operating area                                                                    | 72  |

|---|------|---------|----------------------------------------------------------------------------------------|-----|

|   |      |         | Electrical safe operating area and ESD                                                 | 73  |

|   |      |         | Thermal safe operating area and energy capability                                      | 73  |

|   |      |         | Hot carrier safe operating area and degradation                                        | 73  |

|   |      | 2.6.7   | High level injection and conductivity modulation .                                     | 74  |

|   |      | 2.6.8   | Isolation                                                                              | 74  |

|   |      |         | Low side and high side (or floating) devices                                           | 74  |

|   |      |         | Latch-up, cross-talk and substrate currents                                            | 75  |

|   | Refe | erences |                                                                                        | 75  |

| 3 | TC.  | AD Sir  | mulation and Calibration                                                               | 77  |

|   | 3.1  | Introd  | luction                                                                                | 77  |

|   | 3.2  | Proces  | ss Simulation and Calibration                                                          | 78  |

|   |      | 3.2.1   | The mesh                                                                               | 78  |

|   |      | 3.2.2   | Simulation and calibration                                                             | 82  |

|   |      |         | The epi growth $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 83  |

|   |      |         | 1D Oxidation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$   | 84  |

|   |      |         | $Deposition  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $ | 85  |

|   |      |         | Lithography process                                                                    | 86  |

|   |      |         | Etching                                                                                | 87  |

|   |      |         | 2D Oxidation                                                                           | 87  |

|   |      |         | Implantation, anneal and oxidation                                                     | 89  |

|   |      | 3.2.3   | The end of the process flow                                                            | 92  |

|   |      | 3.2.4   | Performing layout variations                                                           | 93  |

|   |      | 3.2.5   | Simulation of power devices                                                            | 95  |

|   | 3.3  | Device  | e Simulation and Calibration                                                           | 95  |

|   |      | 3.3.1   | From process to device simulation                                                      | 96  |

|   |      | 3.3.2   | Device simulation and calibration                                                      | 100 |

|   | 3.4  | Conclu  | usion                                                                                  | 103 |

|   | Refe | erences |                                                                                        | 104 |

| 4 | Pov  | ver MO  | DS                                                                                     | 105 |

|   | 4.1  | Introd  | luction                                                                                | 105 |

|   | 4.2  | Reduc   | ed Surface Field Effect (RESURF)                                                       |     |

|   |      |         | Analytical expressions                                                                 | 106 |

|   |      |         | Numerical verification                                                                 | 117 |

|   | 4.3  |         | ilicon Limit                                                                           |     |

|   | 4.4  | Which   | n DMOS: n or p, lateral or vertical, RESURF or not?                                    | 126 |

|   |      |         | N or p-type?                                                                           |     |

|   |      |         | Lateral or vertical?                                                                   | 127 |

|          |                                                       |          | RESURF or not?                                      | . 128 |

|----------|-------------------------------------------------------|----------|-----------------------------------------------------|-------|

|          | 4.5 Low-Side, RESURF, n-Type Lateral Drain Extended M |          |                                                     |       |

|          |                                                       | (nLDE    | MOS) without Buried Layers                          | . 130 |

|          |                                                       | 4.5.1    | The "true" RESURF effect at work                    | . 130 |

|          |                                                       | 4.5.2    | Is there a limit to the n-epi doping level ?        | . 134 |

|          |                                                       | 4.5.3    | Using a ndrift ?                                    | . 135 |

|          | 4.6                                                   | Low-S    | ide RESURF nLDEMOS with BLP                         | . 136 |

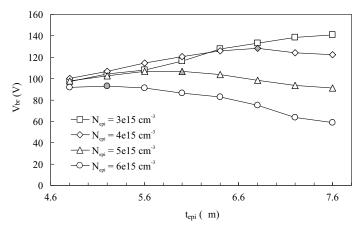

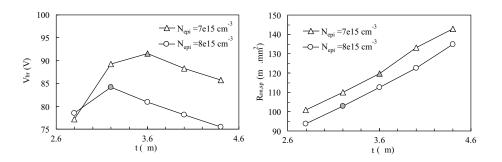

|          |                                                       | 4.6.1    | $V_{br} - R_{on,sp}$ trade-off                      | . 136 |

|          |                                                       |          | Optimizing the n-epi                                | . 136 |

|          |                                                       |          | Optimizing the layout                               | . 137 |

|          |                                                       | 4.6.2    | nLDEMOS with BLP versus Free nLDEMOS                | . 139 |

|          |                                                       |          | Optimal RESURF doses                                | . 139 |

|          |                                                       |          | Safe operating area                                 | . 140 |

|          | 4.7                                                   | High-S   | ide Non-RESURF nLDEMOS with BLN                     | . 144 |

|          | 4.8                                                   | High-S   | ide RESURF nLDEMOS with BLN and BLP $\ . \ .$       | . 147 |

|          | 4.9                                                   | High-S   | ide Integrated Vertical nDEMOS                      |       |

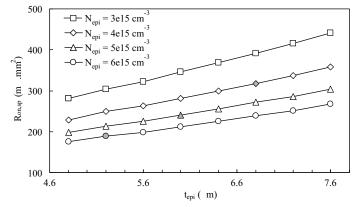

|          |                                                       | 4.9.1    | $V_{br} - R_{on,sp}$ trade-off                      |       |

|          |                                                       |          | Optimizing the n-epi                                |       |

|          |                                                       |          | Optimizing the layout                               |       |

|          |                                                       | 4.9.2    | Safe operating area                                 |       |

|          | 4.10                                                  | -        | ide RESURF pLDEMOS                                  |       |

|          |                                                       |          | Why lateral ?                                       |       |

|          |                                                       |          | Conditions sine qua non on the n-epi                |       |

|          |                                                       | 4.10.3   | pLDEMOS with pwell as pdrift layer                  |       |

|          |                                                       |          | Feasibility of the pwell as pdrift layer            |       |

|          |                                                       |          | Layout variations and main measurement results      |       |

|          |                                                       | 4.10.4   | pLDEMOS with a dedicated pdrift layer               | . 159 |

|          |                                                       |          | Introduction of the pdrift layer in the I3T80H pro- | 150   |

|          |                                                       |          | cess flow                                           |       |

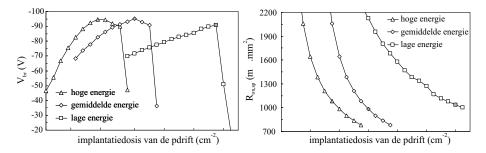

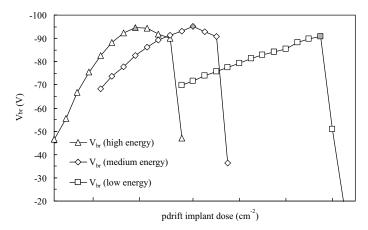

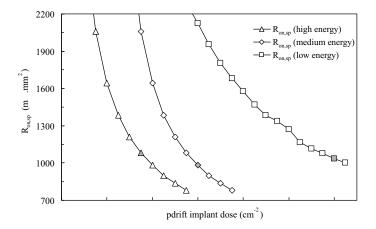

|          |                                                       |          | Determining the pdrift implant conditions           |       |

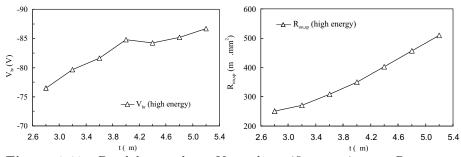

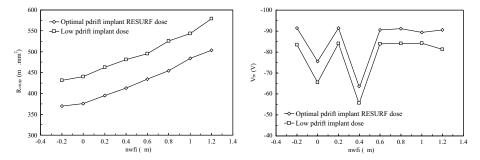

|          |                                                       |          | Layout variations and main measurement results      |       |

|          |                                                       |          | Safe operating area                                 |       |

|          | 4 1 1                                                 | Caral    | Degradation                                         |       |

|          |                                                       |          | usions                                              |       |

|          | nele                                                  | rences . |                                                     | . 109 |

| <b>5</b> | The                                                   | IGBT     | 1                                                   | 175   |

|          | 5.1                                                   |          | uction                                              |       |

|          | 5.2 Breakdown in a nLIGBT without Buried Layers 1     |          |                                                     |       |

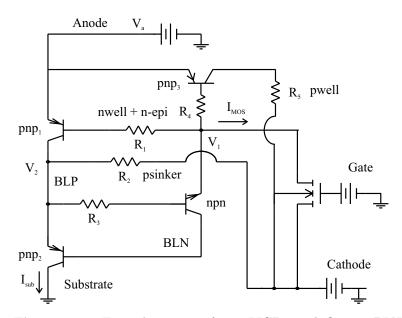

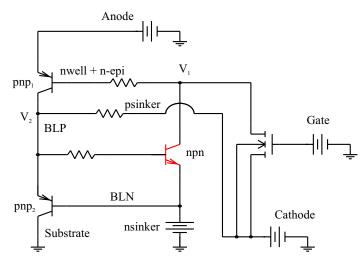

|          | 5.3                                                   |          | ide nLIGBTs with BLN                                |       |

| в | $\mathbf{List}$ | of Ab    | breviations                                                                                                                                   |   | <b>231</b> |

|---|-----------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|---|------------|

| A | $\mathbf{List}$ | of Bas   | sic Symbols                                                                                                                                   |   | 229        |

|   | Refe            | rences . |                                                                                                                                               | • | 225        |

|   | 6.2             | Future   | $e \operatorname{Research} \dots \dots$ |   | 224        |

|   | 6.1             | Overvi   | ew Main Results                                                                                                                               |   | 223        |

| 6 | Syn             | opsis    |                                                                                                                                               |   | 223        |

|   | Refe            | rences . |                                                                                                                                               | • | 222        |

|   | 5.9             |          | sions                                                                                                                                         |   |            |

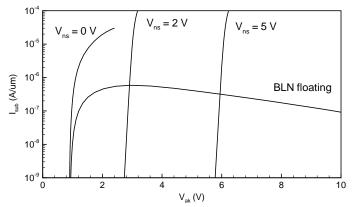

|   |                 | 5.8.3    | Substrate current behaviour                                                                                                                   |   |            |

|   |                 | 5.8.2    | On-state, saturation and latch-up                                                                                                             |   |            |

|   |                 | 5.8.1    | Breakdown                                                                                                                                     | • | 218        |

|   |                 | BLN a    | nd BLP: measurements                                                                                                                          | • | 218        |

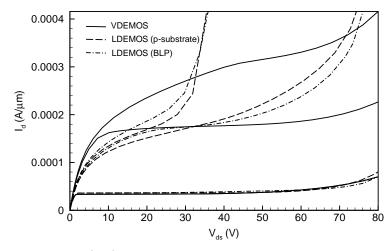

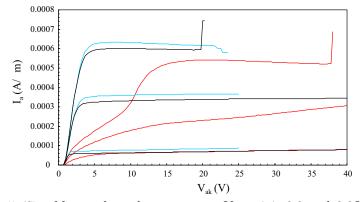

|   | 5.8             | nVDE     | MOS versus standard nLIGBT versus nLIGBT with                                                                                                 | 1 |            |

|   | 5.7             | Integra  | ated Vertical IGBTs                                                                                                                           |   |            |

|   |                 | 5.6.3    | Substrate current                                                                                                                             |   |            |

|   |                 |          | Power dissipation                                                                                                                             |   |            |

|   |                 | 5.6.2    | On-state                                                                                                                                      |   |            |

|   | -               | 5.6.1    | Blocking capability                                                                                                                           |   |            |

|   | 5.6             | P-type   | LIGBTs                                                                                                                                        |   |            |

|   |                 | 5.5.3    | Patterning of the BLN masker                                                                                                                  |   |            |

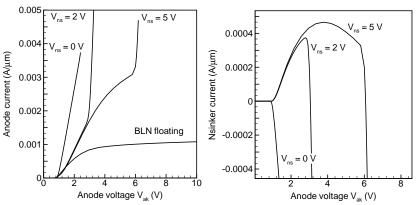

|   |                 |          | Substrate current with a biased BLN                                                                                                           |   |            |

|   |                 |          | Substrate current                                                                                                                             |   |            |

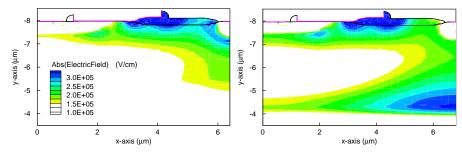

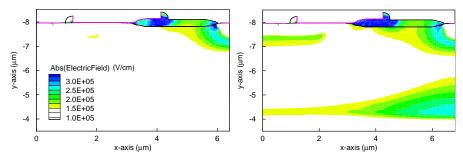

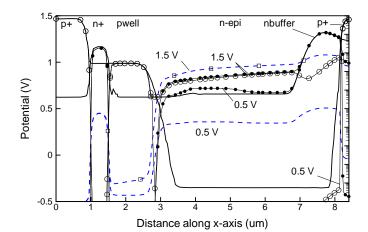

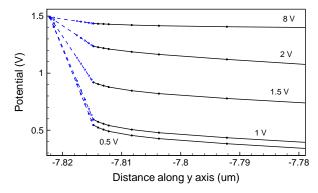

|   |                 |          | Breakdown and on-state                                                                                                                        |   |            |

|   |                 | 5.5.2    | Changing the BLN layer                                                                                                                        |   |            |

|   |                 |          | Contacting the BLN                                                                                                                            |   |            |

|   |                 | 0.0.1    | Substrate current behaviour                                                                                                                   |   |            |

|   | 0.0             | 5.5.1    | The standard process flow                                                                                                                     |   |            |

|   | 5.5             |          | n-Side nLIGBT with BLP and BLN                                                                                                                |   |            |

|   | 5.4             | A Low    | -Side nLIGBT with BLP (standard nLIGBT)                                                                                                       |   |            |

|   |                 |          | Turn-off                                                                                                                                      |   |            |

|   |                 | 0.0.4    | Power dissipation                                                                                                                             |   |            |

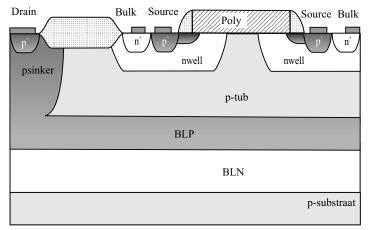

|   |                 | 5.3.2    | A nLIGBT with BLN, psinker, pdrift and nwell .                                                                                                |   |            |

|   |                 |          | Substrate current                                                                                                                             |   |            |

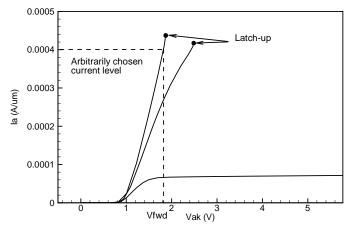

|   |                 |          | Latch-up                                                                                                                                      |   |            |

|   |                 |          | Forward conduction state                                                                                                                      |   |            |

|   |                 | 0.0.1    | Breakdown                                                                                                                                     |   |            |

|   |                 | 5.3.1    | A nLIGBT with a Dedicated nbuffer                                                                                                             |   | 181        |

| С | Calculating Breakdown and Punch-through           |                                                                    |       |  |  |

|---|---------------------------------------------------|--------------------------------------------------------------------|-------|--|--|

|   | C.1                                               | Breakdown of an abrupt $n-p^+$ diode $\ldots \ldots \ldots \ldots$ | . 233 |  |  |

|   | C.2 Punch-through of an abrupt $n^+-n^-p^+$ diode |                                                                    | . 235 |  |  |

|   | C.3                                               | Breakdown of an abrupt n–p diode                                   | . 236 |  |  |

|   | C.4                                               | Punch-through of an abrupt $n^+ – n – p \ diode$                   | . 238 |  |  |

# Nederlandstalige Samenvatting (*Dutch Summary*)

# 1 Inleiding

#### Een beetje geschiedenis

Alhoewel de eerste patenten op de veldeffecttransistor (of MOSFET) reeds in de jaren 30 van de vorige eeuw verschenen, toch was het pas kort na de tweede wereldoorlog dat de eerste bipolaire siliciumtransistor ook echt werd gemaakt. Sommigen noemen deze gebeurtenis de eerste elektronische revolutie, daarbij veronderstellen ze stilzwijgend dat er nog een tweede is. Dit is misschien wat overdreven en de term evolutie is meer gepast. De grootste stappen tijdens deze evolutie waren—van ons perspectief uit gezien—de uitvinding van de thyristor in 1956, de ontwikkeling van de eerste MOS transistor in de jaren 60 (dus het duurde ongeveer 30 jaar om de technische problemen te overwinnen) en van de eerste vermogen-MOS in de jaren 70 en de uitvinding van de IGBT in de jaren 80.

Deze elektronische evolutie heeft twee wegen bewandeld: langs de ene kant de informatieverwerkende technologie met haar typische, constant afnemende transistordimensies. Als gevolg is deze technologie op dit moment in staat om miljarden (!) transistoren op een chip van enkele vierkante centimeter groot te integreren. De snelheid van deze evolutie is verbazingwekkend, de eerste transistor (gefabriceerd in 1947) was enkele vierkante centimeters groot op zich. Maar wat meer is, wie zou nu nog een wereld kunnen voorstellen zonder computers, zonder GSM, zonder satellieten...

Zoals gezegd, de elektronische evolutie volgt ook nog een tweede

spoor die misschien minder zichtbaar is, maar daarom niet minder belangrijk. Het is het ontstaan van de vermogenelektronica die het mogelijk maakt de elektrische energie te controleren en te converteren. Het begon in de jaren 50 met de ontwikkeling van de bipolaire vermogenstransistor. Alhoewel deze vermogentechnologie bijna gelijktijdig met de informatieverwerkende technologie startte, is ze sindsdien er door overschaduwd. Niettemin heeft ze haar eigen weg gevolgd en is ze of zal ze in de nabije toekomst uit de schaduw treden.

Dit is wat sommigen de tweede elektronische revolutie noemen, het ontstaan van de intelligente vermogentechnologie. Het is in feite het samenkomen van beide wegen—de controle van energie met vermogenelektronica en de informatieverwerkende elektronica met de CMOStechnologie. Deze intelligente vermogentechnologieën bestaan reeds en worden gebruikt in talloze toepassingen waar controle op elektrische motoren belangrijk is (van printers tot auto's). De verwachting is dat deze intelligente vermogentechnologieën een even grote maatschappelijke impact zullen hebben als de informatieverwerkende technologieën. Om nog maar te zwijgen over de impact op het milieu, aangezien ongeveer 70 % van alle elektriciteit door 1 of meerdere vermogenstransistoren stroomt. Welk een besparing van elektrisch vermogen is er niet mogelijk indien deze gigantische hoeveelheid energie op een efficiëntere manier kan worden beheerst?

# Hoeveel vermogen? Welke technologie? Welke bouwstenen?

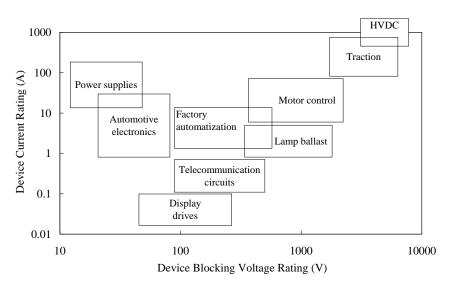

De vorige paragraaf werpt een blik op wat er bestaat in de elektronica: van de CMOS-technologie met de kleine, extreem vlugge transistor tot de vermogenelektronica met de thyristor, traag en extreem groot, maar in staat om duizenden volts te blokkeren en duizenden ampères te controleren. Het spreekt voor zich dat de vermogentechnologie een brede waaier van toepassingen heeft.

Net als de meeste doctoraten, situeert ook dit werk zich in een klein deel van deze brede waaier, namelijk op de grens tussen de CMOStechnologie en de vermogentechnologie; de intelligente vermogentechnologie. In deze vermogentechnologie zullen we ons richten op 1 van de twee klassen van vermogensbouwstenen: de verschillende schakelaars en niet op de klasse van de gelijkrichters (zie Hoofdstuk 2). Natuurlijk is het absurd te spreken over de integratie op chip van bv. de extreem grote thyristor zoals eerder vermeld, die op zich een volledige wafer in

#### 1 Inleiding

beslag neemt (het is onvermijdelijk een discrete bouwsteen, d.w.z. een bouwsteen die niet met andere bouwstenen op een chip is geïntegreerd). Het is duidelijk dat die bouwstenen die geïntegreerd worden op chip een beperkende blokkeerspanning en stroomniveau hebben en dat niet alle bestaande bouwstenen in aanmerking komen voor integratie omdat ze voor welbepaalde, extreme toepassingen werden bedacht.

Dit brengt ons bij het probleem van de vergelijkbaarheid van de verschillende vermogenstransistoren. Dit is belangrijk omdat er een maatstaf nodig is om de efficiëntste transistor te bepalen. Deze maatstaf zal niet enkel afhangen van de spannings- en stroomniveaus, maar ook andere criteria zijn mogelijk. De kwaliteit van de MOS-vermogenstransistoren wordt meestal bepaald door de specifieke aan-weerstand versus de doorslagspanning. Maar wanneer MOS-vermogenstransistoren vergeleken worden met IGBTs dan zullen andere parameters genomen moeten worden aangezien de IGBT een exponentiële stijging van de stroom kent nadat een drempelspanning wordt overschreden. Bovendien zijn er soms andere criteria van tel zoals het bereik van de transistor in de aan-toestand, de afhankelijkheid van de temperatuur, het verval (degradation in het Engels) van de transistor... Deze bouwstenen kunnen ook gebruikt worden om speciale redenen (bv. als zekeringen tegen elektrostatische ontlading) met specifieke eigenschappen en kwaliteiten als gevolg.

Soms bepalen de toepassingen de eigenschappen van de technologie; bv. wanneer chips in een omgeving met hoge temperaturen dienen te werken, zal de silicium op isolator (SOI) technologie verkozen worden. Dit heeft een belangrijk gevolg voor het ontwerp van de vermogenstransistoren aangezien de isolatie nu diëlektrisch i.p.v. met behulp van sperlagen gebeurt. In een junctiegeïsoleerde technologie (zoals in dit werk) gebeurt de isolatie van de verschillende transistoren van elkaar namelijk door het handig gebruik van deze sperlagen. Sommige van de transistoren moeten op een potentiaal staan die hoger is dan die in de omgeving (op de chip). Deze zogenaamde zwevende transistoren hebben extra isolatie lagen nodig die soms moeilijk te realiseren zijn. Dit is trouwens een van de redenen waarom IGBT-transistoren moeilijk te integreren zijn in een junctiegeïsoleerde CMOS-technologie, maar daarover later meer.

Het is dus duidelijk dat een volledig overzicht nodig is van wat er precies nodig is voordat de CMOS-technologie wordt uitgebreid met extra processtappen om de vermogenstransistoren te maken. Niet alleen de verschillende beoogde toepassingen moeten gekend zijn, ook de factor kost kan een rol spelen daar voor sommige applicaties verschillende realisaties mogelijk zijn. Dit is echter iets dat hier niet zal worden bestudeerd. We beperken ons tot het vermelden van het feit dat de basistechnologie waarop verder gewerkt moet worden, een  $0.35 \,\mu\text{m}$  standaard-CMOS, junctiegeïsoleerde technologie is, dat het toepassingsgebied voornamelijk de auto industrie is, dat het spanningsbereik ruwweg tussen de 10 en de 100 V ligt, dat het stroombereik alles onder de 1 A is en dat de schakeltijden zelden sneller dan 10 ns zijn. Dit beperkt het aantal vermogenstransistoren die in aanmerking komen voor integratie tot de MOS-vermogenstransistoren (zie onder andere [Bal96], Hoofdstuk 10). Niettemin zal ook de integratie van de IGBT worden onderzocht.

#### Waarom TCAD?

Het grootste voordeel van Technologie CAD (TCAD) is dat men een bouwsteen kan creëren zonder het ook effectief te moeten maken. Men kan verschillende concepten uitproberen en TCAD voorspelt welke ideeën haalbaar zijn en welke niet. Een ander groot voordeel van TCAD is dat het inzicht geeft in de 2D-distributie (zelfs in 3D) van fysische grootheden. Men kan effectief in een bouwsteen kijken en zien wat er gebeurt wanneer deze of gene spanning aangelegd wordt. Dit heeft reeds meer dan eens geholpen bij het oplossen van problemen in bestaande transistoren. TCAD wordt vaak gebruikt in de literatuur om problemen van allerlei aard uit te leggen, te analyseren en te begrijpen. Een ander voordeel van TCAD is kost. Eens het standaardproces gekalibreerd is in TCAD, kan men met grote betrouwbaarheid nieuwe transistoren ontwikkelen, zelfs indien één of meerdere nieuwe procesmodules gedefinieerd moeten worden. Transistoren kunnen worden ontwikkeld zonder een dure tweede of derde poging, wat de ontwikkelingskosten sterk reduceert. Zelfs de extractie van SPICE-parameters kan al gebeuren voordat de echte transistoren er zijn (wat effectief ook gebeurd is voor de pLDE-MOS, die besproken wordt in dit werk).

Een conditie sine qua non is dat de TCAD-simulaties betrouwbaar zijn. Het nog bestaande scepticisme in de industrie jegens TCAD is hoofdzakelijk tweeledig. Het eerste probleem is de simulatie van 2Ddoperingsprofielen wegens het gebrek aan 2D-ijkmateriaal. Het tweede probleem is de constante evolutie van de transistoren naar kleinere dimensies, waardoor de fysische modellen ook dienen mee te evolueren, wat niet altijd het geval is. Beide bezwaren zijn echter niet van toepassing op het werk dat in dit boek wordt gepresenteerd. Eerst en vooral gebeurt de integratie van vermogenstransistoren in een technologie die reeds goed gekend is (de intelligente vermogentechnologie hinkt verschillende generaties achter op de informatieverwerkende technologie). Ten tweede zijn de vermogenstransistoren van nature groter in dimensie dan hun digitale tegenhangers, waardoor de nood aan fijne 2D-ijking niet zo hoog is. Niettemin blijven ijking en de verwante numerieke problemen een belangrijk punt. Daarom wordt er ook een volledig hoofdstuk aan gewijd (Hoofdstuk 3).

#### Doelstelling

Het doel van dit werk is vermogenstransistoren te ontwerpen en te integreren in een bestaande standaard-CMOS-technologie en nieuwe concepten te bedenken om de efficiëntie van deze transistoren te optimaliseren. De criteria die gebruikt worden, zullen te zijner tijd worden verklaard en zijn hoofdzakelijk heel eenvoudig: de doorslagspanning versus de specifieke aan-weerstand of versus gedissipeerd vermogen. Een belangrijk gegeven dat telkens voorkomt in deze parameters is oppervlakte, welke opnieuw de factor kost is die meespeelt. Hoe kleiner een bouwsteen, hoe minder silicium er wordt gebruikt, hoe kleiner en goedkoper de chip. Om dit te bekomen, moet de vermogensdissipatie tot een minimum worden herleid anders zou te veel warmte op een te kleine oppervlakte gegenereerd worden, wat onherroepelijk tot schade leidt. Indien we de vermogensdissipatie verminderen, wil dit ook zeggen dat we het verlies van energie inperken. Aangezien 60 tot 70% van alle energie door één of meerdere vermogenstransistoren stroomt, betekent dit een efficiëntere controle over de elektrische energie. Of hoe een hoofdzakelijk door kost gedreven motivatie kan leiden tot een ecologisch verantwoorde trend...

## Overzicht

Aangezien de focus van dit werk is het begrijpen, analyseren en ontwerpen van vermogenstransistoren met behulp van TCAD, zullen we ons het meest concentreren op de simulatie van de werking van de verschillende bouwstenen. Daarom geeft Hoofdstuk 2 een overzicht van de fysica nodig voor deze simulaties. Voor een behandeling van de procesen halfgeleidersfysica wordt verwezen naar standaardwerken. Er wordt in Hoofdstuk 2 echter een overzicht gegeven van deze fenomenen die zo belangrijk zijn dat ze niet kunnen ontbreken in een werk over vermogenstransistoren. Over deze vermogenstransistoren bestaan enkele uitstekende werken die de belangrijkste werkingsprincipes en eigenschappen verklaren aan de hand van analytische modellen. Maar, zoals is geschreven in [Bal96, Voorwoord, p. viii] (eigen vertaling):

"Voor een volledig karakterisering van de elektrische eigenschappen van transistoren zijn numerieke technieken die gebruik maken van computerprogramma's broodnodig. Deze programma's kunnen de fundamentele transportvergelijkingen oplossen in 2 dimensies (en soms in 3 dimensies), met tijdsafhankelijkheid indien nodig."

Dit is in een notendop wat gedaan zal worden in de overige hoofdstukken. Maar vooraleer we daarmee beginnen, moeten we het belangrijk punt van de TCAD-simulatie en -ijking behandelen (Hoofdstuk 3). Hoofdstuk 4 en 5 bestuderen dan respectievelijk de vermogen-MOS en de IGBT. Conclusies worden genomen in Hoofdstuk 6 door het vergelijken van de verschillende transistoren met elkaar en met voorbeelden uit de literatuur.

# 2 Fundamentele Beschouwingen

# 2.1 Inleiding

Het is niet de bedoeling van dit boek om een overzicht te geven van alle proces-, halfgeleiders- en transistorfysica nodig voor TCAD-simulaties. We beperken ons tot een verwijzing naar de belangrijkste standaardwerken. Niettemin wordt er een korte schets gegeven van de fysica nodig voor de simulatie van de werking van de bouwstenen. Dit wordt niet gedaan voor de procesfysica daar de klemtoon in dit boek op de werking van de transitoren wordt gelegd.

Vooraleer we beginnen te werken op vermogenstransistoren, wordt er een definitie gegeven van de vermogensbouwsteen, die in 2 klassen wordt opgedeeld: de gelijkrichters en de schakelaars. De gelijkrichters worden slechts kort behandeld met de nadruk op hun doorslagspanning versus doperingsniveau. Dit o.w.v. het feit dat deze eigenschappen gebruikt zullen worden bij het ontwerp van vermogenstransistoren. Dan worden de schakelaars besproken, bestaande uit een classificatie op basis van het type gate. De laatste paragraaf somt een aantal minder bekende fenomenen op die voorkomen bij de studie van geïntegreerde schakelingen. De meeste van deze onderwerpen komen uitgebreid aan bod in de verschillende hoofdstukken over de vermogenstransistoren.

#### 2.2 De fysica

Voor de procesfysica refereren we naar [Sze88] en [CS96], voor de halfgeleidersfysica naar [Wan66] en [Sze81] en voor de transistorfysica in het algemeen naar dit laatste werk en voor de fysica van de vermogenstransistoren in het bijzonder naar [Gha77], [Bal92], [Bal96] en [BGG99].

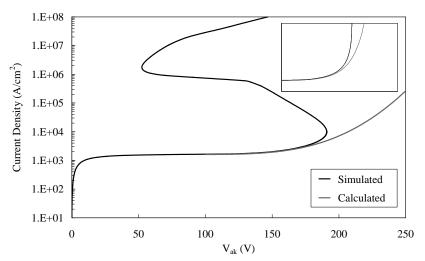

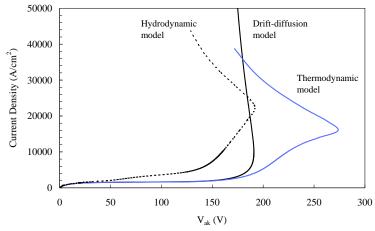

De meeste simulaties van transistoren in dit boek maken gebruik van wat algemeen bekend staat als het drift-diffusiemodel. De continuïteitsvergelijkingen

$$\frac{\partial n}{\partial t} = G_n - R_n + \frac{1}{q} \nabla \mathbf{J}_n \tag{1}$$

$$\frac{\partial p}{\partial t} = G_p - R_p + \frac{1}{q} \nabla \mathbf{J}_p \tag{2}$$

met n en p de elektronen- en gatendichtheid,  $G_n$  en  $G_p$  de elektronen- en gatengeneratiesnelheid en  $R_n$  en  $R_p$  de elektronen- en gatenrecombinatiesnelheid, worden opgelost met behulp van de transportvergelijkingen voor respectievelijk de elektronendichtheidsstroom  $\mathbf{J}_n$  en de gatendichtheidsstroom  $\mathbf{J}_p$ :

$$\mathbf{J}_n = q\mu_n n \mathbf{E} + q D_n \nabla n \tag{3}$$

$$\mathbf{J}_p = q\mu_p p \,\mathbf{E} - qD_p \nabla p,\tag{4}$$

waarin q de elementaire ladingseenheid is, **E** het elektrisch veld,  $\mu_n$  en  $\mu_p$  de elektronen en gatenmobiliteit en  $D_n$  en  $D_p$  de diffusieconstanten van respectievelijk de elektronen en de gaten.

Deze vergelijkingen geven samen met de vergelijkingen van Maxwell een volledige beschrijving van de dynamica van elektronen en gaten in een halfgeleider onder invloed van externe velden. Voor de bouwstenen bestudeerd in dit boek, wordt enkel de vergelijking van Poisson gebruikt.

Soms is het nodig de temperatuur van het rooster in rekening te brengen, met als gevolg dat de uitdrukkingen voor de elektronen- en gatendichtheidsstroom wijzigen, en tevens de warmtetransportvergelijking wordt opgelost. Dit wordt het thermodynamisch model genoemd.

Voor heel kleine bouwstenen volstaat zelfs deze benadering niet en worden ook nog de temperaturen van elektronen en gaten afzonderlijk in rekening gebracht. Dit model staat bekend als het hydrodynamisch model, omdat het stelsel van vergelijkingen analoog is aan dit uit de vloeistoffysica. Dit tijdrovend model wordt echter maar zelden gebruikt bij het ontwerpen van vermogenstransistoren.

#### 2.3 Wat is een vermogensbouwsteen ?

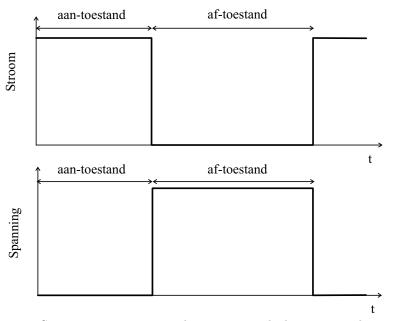

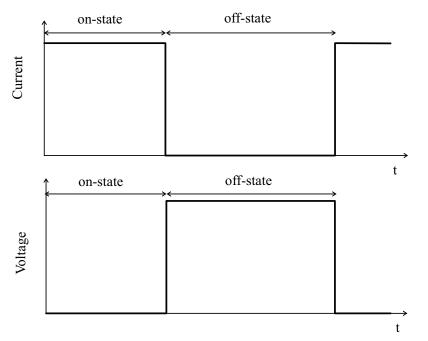

Een vermogensbouwsteen controleert het vermogen dat aan een last wordt gegeven. Dit wordt meestal gedaan door de bouwsteen periodiek te schakelen zodoende stroompulsen te genereren. Het ideale stroomen spanningsverloop worden getoond in figuur 1. Over de ideale vermo-

Figuur 1 Stroom- en spanningsverloop van een ideale vermogensbouwsteen.

gensbouwsteen staat geen spanning wanneer stroom wordt geleid (geen vermogensdissipatie tijdens de aan-toestand), vloeit er geen stroom in de af-toestand (geen vermogensdissipatie tijdens de af-toestand) en is de schakeltijd tussen af- en aantoestand en omgekeerd oneindig vlug (geen vermogensdissipatie tijdens het schakelen). De ideale vermogensbouwsteen verbruikt dus zelf geen vermogen en geeft alle vermogen aan de last (actief of reactief), die capacitief, resistief of inductief kan zijn. De vermogensbouwstenen worden in 2 klassen onderverdeeld: de gelijkrichters (diodes) en de schakelaars. Deze laatsten zijn in staat de hoeveelheid vermogen naar de last te controleren, de eersten zijn dat niet.

#### 2.4 Gelijkrichters

Aangezien de gelijkrichters niet bestudeerd worden in dit boek, wordt maar heel kort een overzicht gegeven van de bestaande types. Niettemin komen diodes in alle mogelijke vormen voor in de structuren van de schakelaars (en dit zeker in junctiegeïsoleerde technologieën, zoals in dit boek). Daarom worden de voor ons zo belangrijke karakteristieke doorslagmechanismen van de elementaire pn- en PT- (uit het Engels *punch-through*) diodes in een grafiek weergegeven.

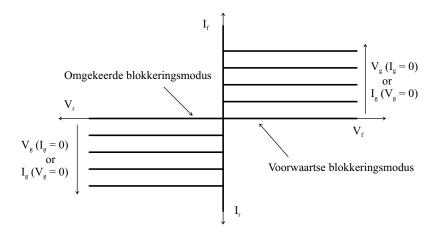

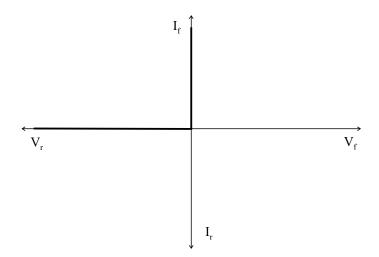

#### De ideale gelijkrichter

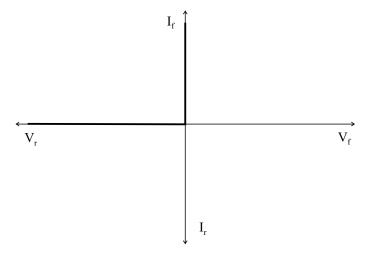

De ideale gelijkrichter blokkeert alle spanning zonder lekstromen in de aftoestand en geleidt zonder weerstand in de aan-toestand, hij is bovendien in staat tussen beide toestanden oneindig vlug te schakelen (figuur 2).

Figuur 2 Uitgangskarakteristiek van een ideale gelijkrichter.

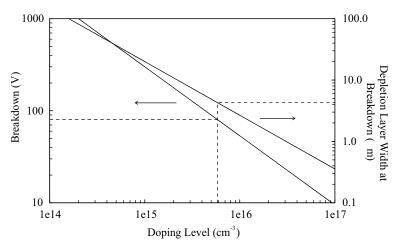

#### De pn-diode

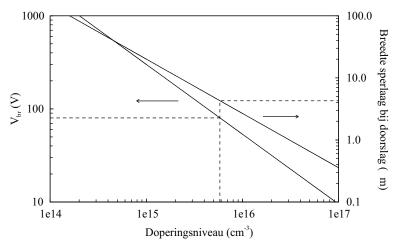

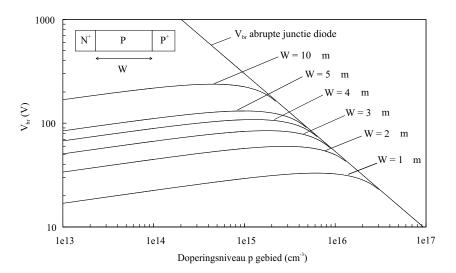

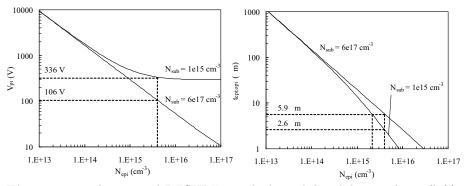

Een echte diode heeft eindige blokkerings-, geleidings- en schakeleigenschappen. Deze worden aangeduid met de volgende parameters: blokkeringsspanning  $V_{br}$ , voorwaartse spanningsval tijdens de aan-toestand  $V_{on}$ , schakeltijd van de af- naar de aan-toestand  $t_{on}$  en omgekeerd  $t_{off}$ . Bovendien is er een lekstroom tijdens de af-toestand, waardoor er ook vermogensdissipatie is tijdens de af-toestand. Als voorbeeld van een abrupte n<sup>+</sup>p-diode wordt op figuur 3 een 80 V diode gegeven. Uit de figuur leidt men af dat het maximale doperingsniveau  $5.8e15 \text{ cm}^{-3}$  is en dat de breedte van de sperlaag in dit geval  $4.3 \,\mu\text{m}$  is.

**Figuur 3** Doorslagspanning  $V_{br}$  en breedte van de sperlaag bij doorslag als functie van het doperingsniveau van het laag gedopeerd gebied van n<sup>+</sup>p-diode.

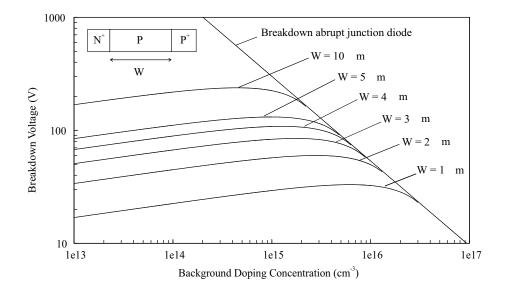

## De PT-diode

Indien in het vorige voorbeeld de sperlaag in het p-gebied bij een bepaalde spanning een p<sup>+</sup>-gebied tegenkomt, dan stopt de sperlaag virtueel en groeit het elektrisch veld verder in het volledige p-gebied. Het gevolg is een lagere doorslagspanning (figuur 4).

**Figuur 4**  $V_{br}$  voor een abrupte junctie diode en voor PT-diodes met verschillende breedtes. De inzet toont een PT-diode.

Het belang van deze PT-diodes ligt in het feit dat men in een gebied met een kleinere dimensie als de breedte van de sperlaag bij een abrupte  $n^+p$ -diode, dezelfde spanning kan bekomen *indien men het doperings-niveau van het laag gedopeerd gebied verlaagt*. Als voorbeeld nemen we opnieuw een 80 V diode, waar bv. een breedte van 3 µm voldoende is indien men het doperingsniveau verlaagt tot  $1.8e15 \text{ cm}^{-3}$ .

#### 2.5 Schakelaars

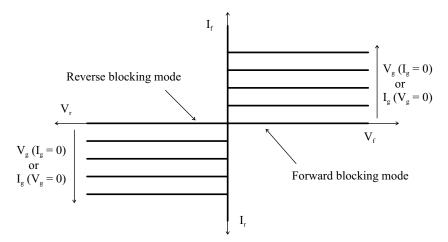

De schakelaar heeft één contact meer als de diode, namelijk de poort of gate die de uitgangsstroom controleert. De ideale uitgangskarakteristieken van een schakelaar worden geschetst in figuur 5.

Figuur 5 Uitgangskarakteristieken van een ideale schakelaar.

#### Stroomgecontroleerde schakelaars

De bipolaire vermogenstransistor is de allereerste vermogensschakelaar ooit gemaakt. Zijn gebruik nam echter vanaf de jaren 70 af door de concurrentie van de MOS-vermogenstransistoren. De bipolaire vermogenstransistor wordt echter wel nog gebruikt in welbepaalde toepassingen.

De tweede oudste vermogensschakelaar die stroomgestuuurd is, is de thyristor. Deze schakelaar bestaat uit 4 lagen verschillend gedopeerd silicium en is de allerbeste geleider uitgedrukt in hoeveelheid stroom per oppervlakte-eenheid. Het grootste nadeel is dat de controle over de stroom door de gate wordt verloren bij grote stroomdichtheden. De thyristor wordt vooral gebruikt in omstandigheden waar extreem grote spanningen en stromen voorkomen.

#### Spanningsgecontroleerde schakelaars

12

De sperlaag-veldeffecttransistor (JFET of SIT) is een schakelaar die stroom geleidt wanneer er geen signaal op de gate is, wat maakt dat deze schakelaar maar in welbepaalde toepassingen wordt gebruikt.

De MOS-vermogenstransistor kwam er als gevolg van de successen van de digitale CMOS-transistoren, de nMOS en de pMOS. Deze MOS-vermogenstransistoren hebben hun bipolaire tegenhangers in vele toepassingsgebieden uit de markt geconcurreerd. Dit komt omdat de MOS-vermogenstransistor een hogere ingangsimpedantie heeft, sneller is wegens de unipolariteit, de aan-weerstand een negatieve temperatuursafhankelijkheid heeft (waardoor het veilig wordt om deze transistoren in parallel te plaatsen) en het een groot spanningsbereik (SOA) heeft.

De bipolaire transistor met geïsoleerde gate (IGBT) is een schakelaar die de beste eigenschappen van de bipolaire en van de MOSvermogensschakelaars probeert te combineren: een lage voorwaartse spanningsval bij geleiding en een hoge ingangsimpedantie. Jammer genoeg erft heeft hij een kleinere SOA, is hij trager dan de MOS en heeft hij een positieve temperatuursafhankelijkheid.

Een laatste type van spanningsgecontroleerde schakelaars is de MOSgecontroleerde thyristor, die net als de thyristor meestal voorkomt in toepassingen voor extreme omstandigheden.

## 2.6 Fundamentele concepten omtrent geïntegreerde vermogensschakelaars

De bedoeling van deze paragraaf is een overzicht te geven van de belangrijkste concepten die gebruikt worden bij het ontwerpen van vermogenstransistoren in geïntegreerde schakelingen. De meeste van deze concepten komen uitgebreid aan bod in de verschillende hoofdstukken over de vermogenstransistoren.

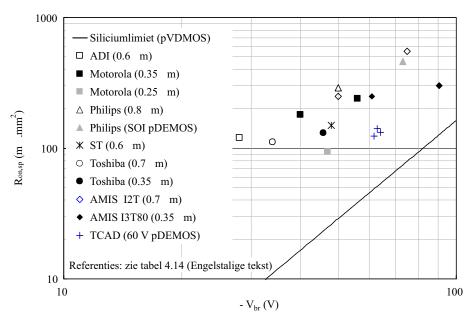

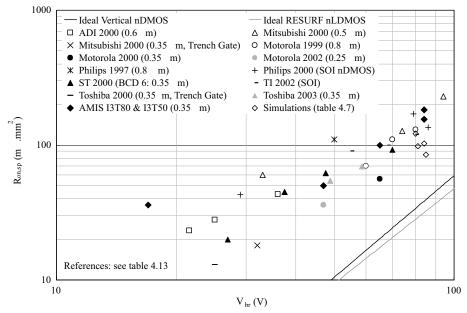

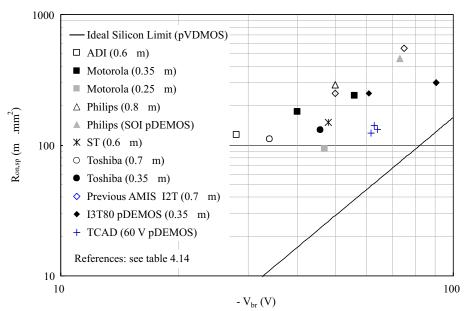

#### De siliciumlimiet

De siliciumlimiet is de analytische uitdrukking voor de specifieke aanweerstand  $R_{on,sp}$  in functie van de doorslagspanning  $V_{br}$  voor een ideale MOS-vermogenstransistor. Indien beide parameters voor een bestaande transistor worden uitgezet in een grafiek samen met de siliciumlimiet en samen met de parameters van andere bestaande transitoren van concurrenten, dan kan men de beste transistor voor een bepaalde spanning in één oogopslag eruit halen (nl. deze die het dichtst bij de limiet ligt). Het dient vermeld te worden dat er verschillende siliciumlimieten bestaan, nl. voor de verschillende vormen van de MOS-vermogenstransistor (verticaal, lateraal, RESURF, SOI, superjunctie of  $\text{COOLMOS}^{TM}$ ...).

#### **RESURF-effect**

Het RESURF-effect (uit het Engels REduced SURface Field) is een 2Dtechniek waarbij de distributie van de elektrische velden op een optimale manier gespreid worden. Het is één van de meest gebruikte technieken bij het ontwerp van vermogensbouwstenen. Aanvankelijk werd het gebruikt in diodes, maar tegenwoordig wordt het in bijna elke vermogenstransistor en op verschillende manieren (met verschillende lagen in de zogenaamde superjunctietransistoren, op SOI, in 3D...) toegepast.

#### PT- en RT-doorslag

PT- en RT- (uit het Engels *Reach-Through*) doorslag zijn verschillende fenomenen. PT-doorslag komt voor in een PT-diode wanneer het kritische elektrische veld wordt bereikt aan de pn-junctie. RT-doorslag daarentegen komt voor in een pnp- of npn-structuur, waarbij de sperlaag komende van één van de juncties de andere raakt. Dan wordt een pad gecreëerd die geleiding veroorzaakt. Dit mechanisme kan dus voorkomen lang vòòr dat het kritische elektrische veld wordt bereikt. Niettemin worden beide termen in de literatuur vaak door elkaar gebruikt.

#### Tweede doorslag, terugslag en thermische instabiliteit

Vroeger gebruikte men de term tweede doorslag wanneer men thermische instabiliteit beschreef (bv. in [Gha77]), maar tegenwoordig wordt de term meestal gebruikt om een plotse reductie van de doorslag in de aan-toestand (i.v.m. de doorslag in de af-toestand) aan te duiden. Deze tweede doorslag kan gepaard gaan met een terugval in de spanning, met een negatieve weerstand als gevolg. Dit is wat men in het Engels *snapback* (terugslag) noemt. De term thermische instabiliteit wordt enkel nog gebruikt bij temperatuursfenomenen van destructieve aard.

#### Kirk-effect en adaptieve RESURF

Het Kirk-effect wordt normaal beschreven in een bipolaire transistor [Sze81, p.145]. Het komt echter ook voor in MOS-vermogenstransistoren, en in het bijzonder in laterale structuren die gebruik maken van het RESURF-effect. Het gevolg is een afname van het spanningsbereik in de aan-toestand. Een mogelijke oplossing is wat men noemt "adaptieve RESURF", waarmee de verschuiving van het elektrisch veld naar de drain toe wordt verholpen door een verhoging van het doperingsniveau in de buurt van het draincontact.

# SOA

De SOA (staat voor *Safe Operating Area*) is gedefinieerd als het spanningsgebied waarbinnen de schakelaar op een veilige manier kan gebruikt worden. Dit is een vage definitie en men onderscheidt dan ook drie verschillende SOAs:

• Elektrische SOA en ESD

Een schakelaar kan gedurende een heel korte tijd (ns tot  $\mu$ s) gebruikt worden in het bereik van de uitgangskarakteristiek na de doorslag en na de terugslag. Bepaalde schakelaars worden zelfs speciaal ontworpen om deze eigenschap te benadrukken. Deze worden bijvoorbeeld gebruikt in ESD (ElectroStatic Discharge) protectiecircuits. Deze bouwstenen worden hier niet besproken.

• Thermische SOA en energetisch opvangvermogen

Wanneer de stroompulsen langer duren ( $\mu$ s tot ms) dan worden temperatuurseffecten belangrijk, waardoor er gevaar op thermische instabiliteit ontstaat. Sommige bouwstenen worden speciaal ontworpen om een zo groot mogelijke energiestoot op te vangen, bv. bij het uitschakelen van een inductieve last. Ook dit soort van bouwstenen wordt niet besproken in dit boek.

• Hetelading-SOA en degradatie

Wanneer een schakelaar niet wordt gebruikt in de extreme omstandigheden zoals in beide bovenstaande voorbeelden, dan is de SOA meestal nog kleiner dan de elektrische en thermische SOA. Zeker in schakelaars met een MOS-gate is dit het geval, waar de ladingen die door het kanaal stromen na verloop van tijd het oxidelaagje vervuilen. Deze vervuiling veroorzaakt verschuivingen in de elektrische eigenschappen van de transistor. Dit is wat men noemt degradatie, die gekarakteriseerd wordt op basis van stressmetingen. Het toegelaten spanningsbereik wordt dan bepaald aan de hand van extrapolatie van de meest verslechterende parameter (en dit kan verschillend zijn naargelang de spanningen op de verschillende contacten).

#### Hoge injectie en geleidingsmodulatie

Injectie van minoritairen in een laag gedopeerd p- of n-gebied kan zo hoog zijn dat de elektronen en gaten in een hogere concentratie aanwezig zijn dan het oorspronkelijk doperingsniveau. De weerstand in dit gebied vermindert dan aanzienlijk, i.e. geleidingsmodulatie. Dit fenomeen zorgt ervoor dat in vele vermogensbouwstenen een lage voorwaartse spanningsval in de aan-toestand leidt tot hoge stroomniveaus.

#### Isolatie

Het is goed mogelijk dat men een geïntegreerde vermogensbouwsteen ontwerpt met een interne doorslagspanning van bijvoorbeeld meer dan 80 V, maar dat er toch problemen optreden bij lagere spanningen. Dit komt omdat men ervoor moet zorgen dat de elektrische isolatie van deze geïntegreerde bouwsteen op zijn minst de doorslagspanning ervan moet aankunnen. Verder moeten sommigen geïntegreerde bouwstenen in hun geheel (d.w.z. op alle contacten tegelijkertijd) op een spanning staan die hoger is dan de spanningen in de directe omgeving. Dit noemt men de zwevende bouwstenen en deze hebben vaak een isolatiestructuur die heel wat uitgebreider is dan die van hun niet-zwevende tegenhangers.

# 3 TCAD-Simulatie en -IJking

# 3.1 Inleiding

Technologie-CAD (TCAD) gebruikt fysische modellen ten einde een volledig productieproces stap voor stap, en daarna de werking van de gesimuleerde bouwstenen, te simuleren. Deze proces- en bouwsteensimulatoren brengen de eigenschappen van deze bouwstenen op een niet-uniform, discreet raster van punten aan (in 1, 2 of zelfs 3 dimensies) om de differentiaalvergelijkingen die de verschillende fysische processen beschrijven numeriek op te lossen. Dit hoofdstuk bestaat uit twee delen, het eerste beschrijft de ijking en rasterproblematiek in de processimulator, het tweede doet dit voor de bouwsteensimulator.

## 3.2 Processimulatie en -ijking

#### Het raster

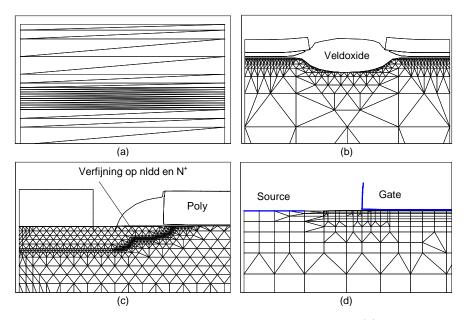

Het raster zorgt voor het grootste deel van de problemen gedurende TCAD-werk. De gebruiker wil een raster dat zo ruw mogelijk is om

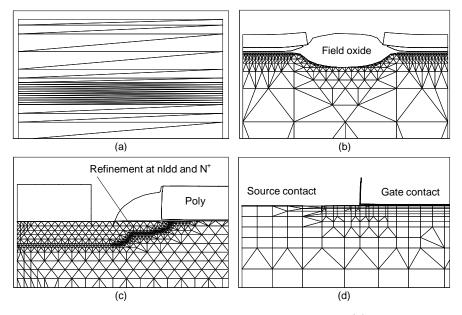

**Figuur 6** Evolutie van het raster doorheen de simulatie: (a) 1D in proces simulatie, (b) eerste proces stap in 2D, (c) op het einde van het proces en (d) nieuw raster voor simulatie van de werking van de transistor.

de simulatietijd te beperken, maar het moet wel fijn genoeg blijven om correcte resultaten af te leveren.

Ter illustratie van deze problematiek zal een simpele nMOS gesimuleerd worden als leidraad doorheen dit hoofdstuk. Omdat de simulaties gebaseerd zijn op het bestaande  $0.35 \,\mu\text{m}$  CMOS proces van AMIS, worden de assen van vele figuren weggelaten door de confidentiële aard ervan. Deze werkwijze ondermijnt het doel van deze discussie geenszins.

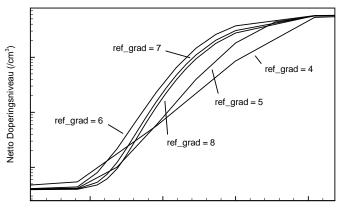

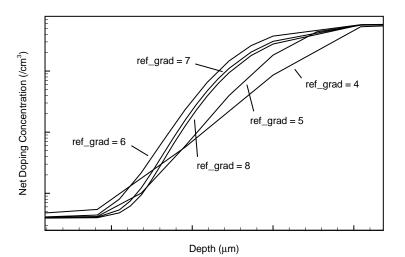

In het begin van de simulatie is het raster nog in 1 dimensie (d.w.z. een verzameling lijnen in een rechthoek). Wanneer het nodig wordt de tweede dimensie mee in rekening te brengen (bij de definitie van een masker), dan schakelt de simulator automatisch over op 2 dimensies. Het raster wordt enkel verfijnd daar waar nodig (aan een junctie, gradiënt in doperingsniveau, oneffenheden op de Si/SiO<sub>2</sub> grens...) met behulp van welbepaalde parameters (Refinejunction, RefineGradient, RefineBoundary...) uit de ISE-software. Deze verfijning gebeurt door de definitie van rechthoeken in het simulatiedomein gedurende de simulatie (bijvoorbeeld net voor een implantatie), zie figuur 6 voor enkele voorbeelden. Een voorbeeld van de invloed van een dergelijke parameter op het simulatieresultaat wordt gegeven in figuur 7.

Figuur 7 Invloed van de verfijning van het raster (Refgrad) op een doperingsprofiel.

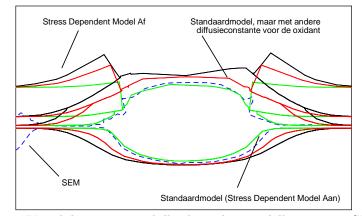

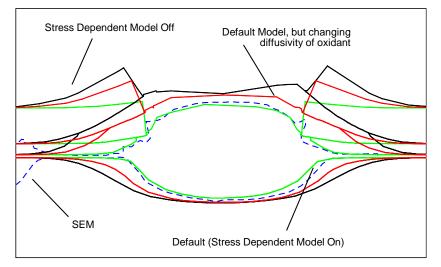

Figuur 8 Vergelijking van verschillende oxidatiemodellen met een SEM-foto.

#### Simulatie en ijking

Het zou ideaal zijn indien we zouden beschikken over ijkmateriaal (SIMS, SEM...) na elke gesimuleerde processtap. Jammer genoeg is dit niet haalbaar vanwege de kost en moeten we ons beperken tot enkele belangrijke stappen. Zoals gezegd in het inleidend hoofdstuk, beschikken we niet over 2D-doperingsprofielen en werken we dus steeds met SIMS-profielen in 1D. De veldoxidatie kunnen we wel kalibreren met behulp van SEM-foto's in 2D. Daartoe zijn verschillende oxidatiemodellen in de software opgenomen (met elk hun eigen verzameling modelparameters). In figuur 8 kan men zien dat het standaardmodel het veldoxide nagenoeg correct simuleert.

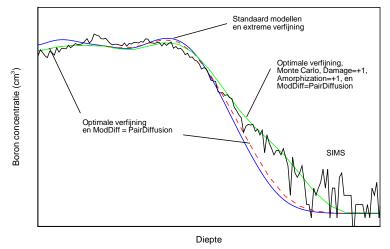

**Figuur 9** Vergelijking van het SIMS-profiel van de pwell na gate-oxidatie met verschillende gesimuleerde profielen.

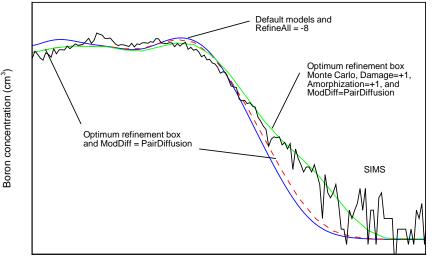

De SIMS worden genomen na de eerste temperatuurstap die volgt op de implantatie of op het einde van het proces (d.w.z. na de laatste hoge temperatuurstap, na dewelke de profielen niet meer veranderen). Ook hier zien we de invloed van de verschillende implantatiemodellen (standaard, i.e., m.b.v. analytische uitdrukkingen; ofwel met Monte Carlo simulatie) in combinatie met de verschillende diffusiemodellen (indien bv. schade aan het rooster in rekening wordt gebracht met het model Damage = +1, zie figuur 9).

Alle overige processtappen (maskers, etsen, deposities) gebeuren geometrisch en hun commando's zijn dan ook veel minder uitgebreid dan deze voor de implantatie-, de oxidatie- en de diffusieprocessen. Het einde van de processimulatie wordt bereikt bij de laatste hoge temperatuurstap in het productieproces.

#### 3.3 Bouwsteensimulatie en -ijking

#### Van proces- naar transistorsimulatie

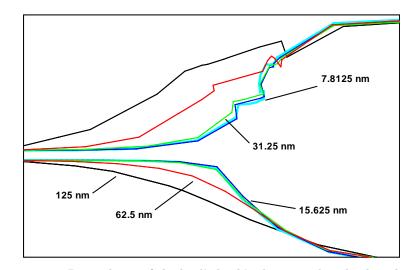

Vooraleer we de werking van de nMOS-transistor simuleren, moeten we de structuur een nieuw raster geven. Dit is broodnodig omdat het raster dat gebruikt wordt voor de processimulatie niet fijn genoeg is in het ene gebied en dan weer te fijn in een ander voor de transistorsimulatie. Een voorbeeld daarvan zien we in figuur 6. Onzichtbaar in deze figuur is het ultra fijne rooster ( $\sim 2 \text{ nm}$ ) in het kanaal, dat nodig is voor de transistor

**Figuur 10**  $I_d(V_{gs})$  voor een nMOS met getekende kanaallengte van 2 µm: SPICE-simulaties versus TCAD-simulaties.

simulatie (figuur 6, (d)), maar dat overbodig is voor de simulatie van het pwell-profiel gedurende de processimulatie (figuur 6, (c)).

#### Transistorsimulatie en -ijking

De transistor<br/>simulatie eist veel minder ijkwerk aangezien de werking van een transistor i<br/>dealiter fabrieksonafhankelijk is. De belangrijkste uitzondering hierop is verbonden aan het productie<br/>proces, nl. de werkfunctie van de gate. Deze dient gekalibreerd te worden m.b.v. de gemeten<br/> $V_t$  waarden.

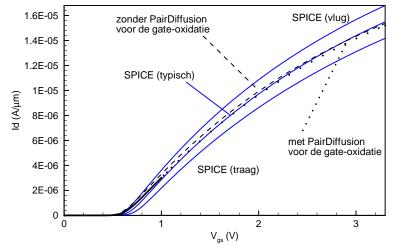

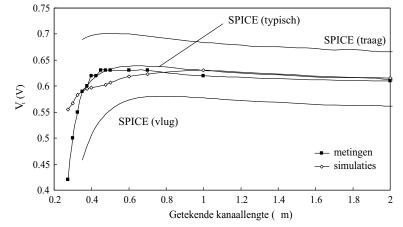

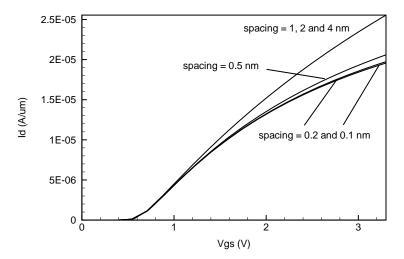

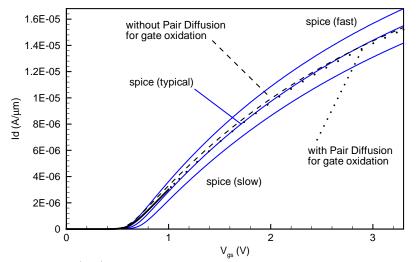

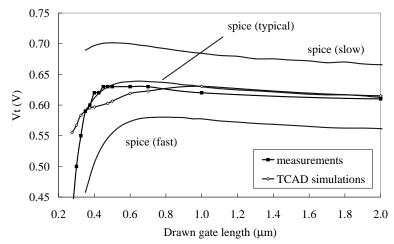

Indien de gemeten elektrische karakteristieken van een transistor verschillend zijn dan de gesimuleerde, dan dient in de eerste plaats gekeken te worden naar eventuele fouten tijdens de processimulatie. Een voorbeeld hiervan wordt gegeven in figuur 10, waar SPICE-simulaties worden vergeleken met TCAD-simulaties. Het is duidelijk te zien dat door gebruik te maken van een ander model voor de gate-oxidatie, er een invloed is op de transferkarakteristiek. Niettemin is deze invloed erg klein en dient het complexere, meer tijdrovend oxidatiemodel enkel gebruikt te worden indien dit vereist is. Dit is bijvoorbeeld het geval indien men korte-kanaalseffecten wil bestuderen. In figuur 11 ziet men dat men de correcte  $V_t$  waarde niet kan simuleren voor kleine kanaallengtes door enkel gebruik te maken van de standaardmodellen, zoals werd gedaan voor de TCAD-simulaties op deze figuur.

**Figuur 11**  $V_t$  in functie van getekende kanaallengte: vergelijking tussen metingen, SPICE- en TCAD-simulaties.

#### 3.4 Besluit

In dit hoofdstuk werd in de processimulatie en in de transistorsimulatie enkel gebruik gemaakt van de standaardmodellen met een minimum aan ijkwerk. Indien men problemen als de korte-kanaalseffecten wenst te simuleren, dan zal men ook complexere modellen tijdens de processimulatie dienen te gebruiken, met een navenante stijging van de hoeveelheid ijkwerk als gevolg. Voor het werk dat gepresenteerd wordt in dit boek, zal dit echter nooit het geval zijn aangezien we in de eerste plaats eerder grote transistoren simuleren en in de tweede plaats TCAD zullen gebruiken als hulpmiddel bij het onderzoeken van trends in proces- en lay-outvariaties en bij het uitproberen van nieuwe ideeën en concepten. Net zoals in de literatuur, zullen we ook hier TCAD gebruiken bij het analyseren, begrijpen en voorspellen van problemen en trends, maar niet voor het voorspellen van absolute, exacte waarden.

# 4 Vermogen-MOS

#### 4.1 Inleiding

Eén van de eerste referentiewerken over vermogensbouwstenen, geschreven in 1977 door S.K. Ghandhi [Gha77], behandelt de MOS-vermogenstransistor niet en spreekt enkel over de bipolaire vermogenstransistor en de thyristor. Daartegenover staat dat één van de meest recente standaardwerken, geschreven in 1996 door B.J. Baliga [Bal96], de bipolaire vermogenstransistor enkel behandelt als inleiding tot een bepaald type MOS-vermogenstransistor, nl. de IGBT. Dit illustreert de evolutie van de vermogenstransistoren over een tijdspanne van 20 jaar en toont het belang aan van de introductie van de MOS-gate in deze bouwstenen. De stroomgestuurde gate en bijhorende complexe ingangscircuiten voor de bipolaire transistoren werd vervangen door een spanningsgestuurde gate met een veel eenvoudiger ingangscircuit. De MOS-transistor heeft bovendien een veel vluggere schakelsnelheid (wegens zijn unipolariteit), heeft een negatieve temperatuursafhankelijkheid (hoe warmer, hoe minder stroom wordt geleid, wat ideaal is om deze transistoren in parallel te plaatsen), en is veel minder onderhevig aan tweede doorslag.

Omdat de MOS-gate zijn oorsprong kent in de digitale CMOS-technologieën, is de eerste MOS-vermogenstransistor, een soort van uitgebreide MOS of DEMOS (*Drain Extended* MOS). Daarna werd de dubbelediffusie-MOS (DMOS) uitgevonden, zo genoemd omdat het kanaal samen met de source-gebieden worden geïmplanteerd en gediffundeerd na de depositie van de poly-gate. De volgende belangrijke stap was de introductie van het RESURF-effect, dat behandeld wordt in de volgende paragraaf. Het is één van de meest belangrijke technieken voor het ontwerpen van vermogensbouwstenen geworden (niet enkel MOS-transistoren).

De zeer belangrijk siliciumlimiet, die dient als een waardemeter voor de MOS-vermogenstransistoren wordt besproken in het volgende luik. Hierop volgt een korte uiteenzetting over de verschillende vormen en types van de MOS-vermogenstransistoren, die daarna elk op hun beurt bestudeerd worden. De conclusie vergelijkt de bekomen MOS-vermogenstransistoren met deze gevonden in de literatuur.

#### 4.2 **RESURF-effect**

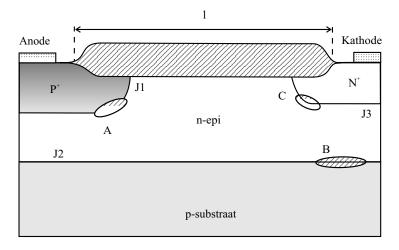

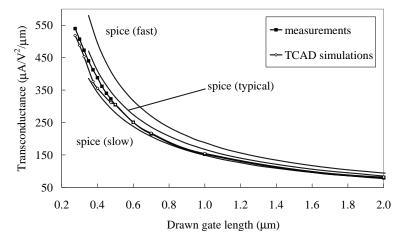

Het RESURF-effect werd bij toeval ontdekt in 1979 [AV79] bij de studie van diodes (figuur 12).

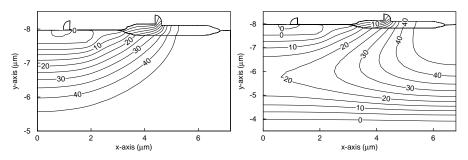

Deze basisstructuur bestaat uit 2 diodes: een verticale diode  $(n^+-n-epi-p-substraat)$  en een laterale diode  $(p^+-n-epi-n^+)$ . De doorslagspanning in een dergelijke structuur is een samenspel tussen verschillende 2D-effecten. Samenvattend kunnen we stellen dat het RESURF-effect erop neerkomt dat de doorslag (i.e., bij een negatief spanningsverschil tussen anode en kathode) niet gebeurt op plaats A in figuur 12, wat normaal gezien gebeurt wanneer de epilaag dik genoeg is in vergelijking met de lengte l; maar dat het elektrisch veld vanaf een bepaalde spanning terzelfder tijd op de plaatsen A, B en C zal groeien, waar-

Figuur 12 Een RESURF-diode.

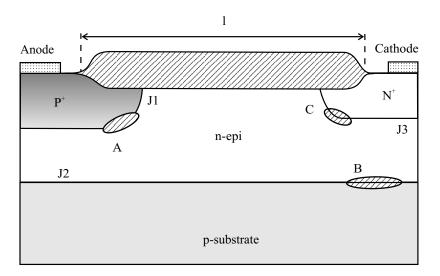

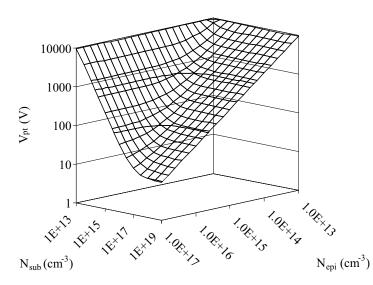

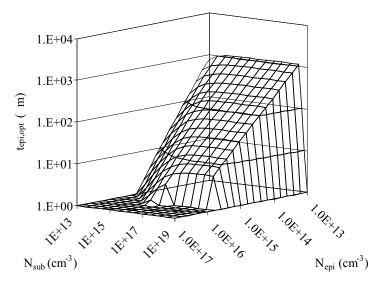

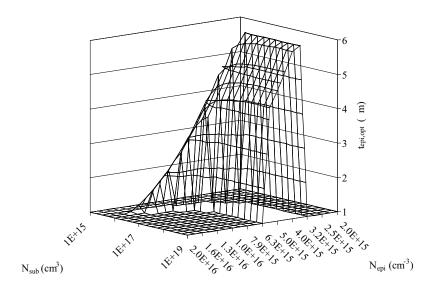

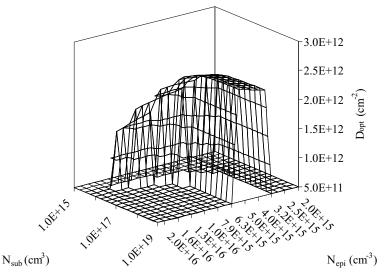

door een doorslagspanning wordt verkregen die veel groter is dan verwacht. Deze doorslagspanning zal dan bepaald worden door het laagst gedopeerd gebied in de structuur, wat dus het p-substraat kan zijn, en die dus een veel hogere spanning aan kan als wat men van de hoger gedopeerde epilaag kan verwachten. De voorwaarde om een optimale RESURF-werking te bekomen, is dat de epidosis een welbepaalde waarde ( $D_{opt} = t_{epi,opt} \times N_{epi}$  met  $t_{epi}$  en  $N_{epi}$  respectievelijk de dikte en het doperingsniveau van de epilaag) heeft die afhankelijk is van het doperingsniveau van het substraat. De werking van het RESURF-effect zal verder geïllustreerd worden bij de behandeling van de verschillende laterale RESURF-vermogenstransistoren.

#### 4.3 De Siliciumlimiet

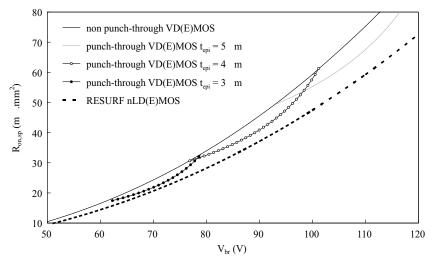

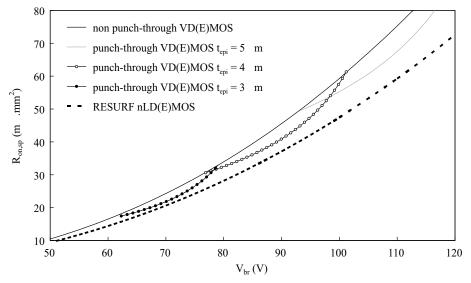

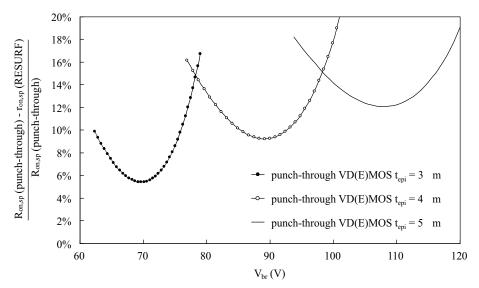

De siliciumlimiet is de analytische uitdrukking van de specifieke aanweerstand als functie van de doorslagspanning voor een geïdealiseerde MOS-bouwsteen. Op deze manier kunnen beide belangrijkste elektrische parameters van de MOS-vermogenstransistor in één grafiek tegenover elkaar uitgezet worden en vergeleken worden met de ideale siliciumlimiet. Deze grafiek doet dus dienst als maatstaf voor alle bestaande MOS-vermogenstransistoren: in één oogopslag kan men zien voor welke doorslagspanning welke transistor het best presteert, nl. deze die zich het dichtst bij de siliciumlimiet bevindt.

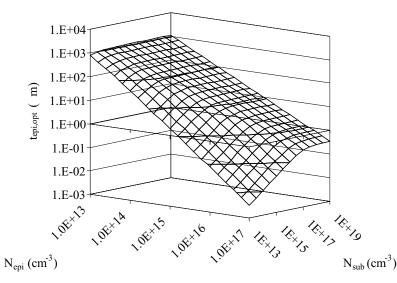

Er bestaan verschillende siliciumlimieten naargelang de vorm (lateraal of verticaal, RESURF of niet), de aard (n- of p-type), en zelfs de

**Figuur 13** De siliciumlimieten voor NPT en PT nVD(E)MOS en voor de laterale RESURF nD(E)MOS.

technologie (SOI). In figuur 13 worden de verschillende limieten getoond die voor ons van belang zijn.

Het moet echter gezegd dat deze theoretische limieten steunen op een aantal benaderingen, waardoor de schijnbare conclusie dat de verticale PT-transistoren niet veel onder moeten doen voor de laterale RESURFtransistoren (en zelfs beter doen voor dunnere epilagen) met de nodige voorzichtigheid dient bejegend te worden. Zoals zal blijken uit de paragrafen die deze verschillende transistoren bestuderen, zullen andere fenomenen die niet in rekening werden gebracht bij deze theoretische beschouwingen bepalen welke transistor nu de betere is. Tevens zullen we zien dat er ook andere criteria als de doorslagspanning en de specifieke aan-weerstand een doorslaggevende rol kunnen spelen.

# 4.4 Welke DMOS: n of p, lateraal of verticaal, RESURF of niet ?

#### N- of p-type ?

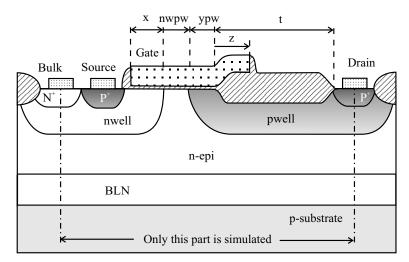

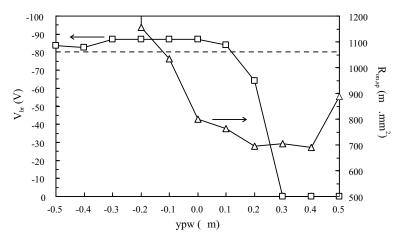

Aangezien de mobiliteit van elektronen ongeveer drie maal hoger is dan die van gaten in silicium, hebben de n-type transistoren een aanweerstand die drie maal beter is dan die van de p-types. Of, in andere woorden, om eenzelfde hoeveelheid stroom te genereren moeten de ptype transistoren ongeveer driemaal groter zijn dan de n-types. Het is duidelijk dat de n-type transistoren verkozen worden boven de p-types. Niettemin zijn de p-type transistoren belangrijk voor circuitontwerpers daar ze een oplossing bieden voor sommige circuitproblemen waar anders 2, 3, of meerdere n-type transistoren voor nodig zijn (dit komt door het feit dat p-type transistoren zich in de aan-toestand bevinden wanneer  $V_{gs} < V_t < 0$  V). Het verlies aan siliciumoppervlakte wordt dan grotendeels (zo niet volledig) gecompenseerd. De pDMOS wordt normaal gezien als zwevende transistor gebruikt, wat betekent dat het volledige gebied waarin de transistor zich bevindt op een hogere potentiaal staat dan de omliggende gebieden.

#### Lateraal of verticaal ?

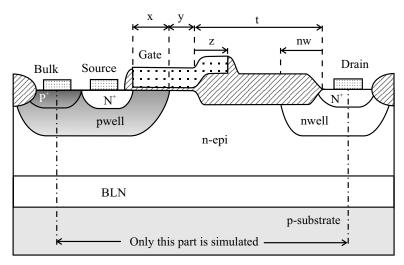

Men spreekt van verticale bouwstenen in een geïntegreerde schakeling wanneer (een deel van) de drain zich onder de transistor bevindt. De stroom wordt daarna wel gerecupereerd aan de oppervlakte m.b.v. begraven lagen (*buried layers*) en pluggen die deze lagen opnieuw met de oppervlakte verbinden via een laag resistief pad.

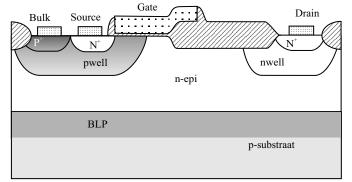

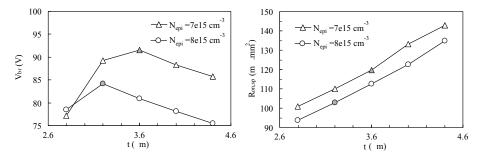

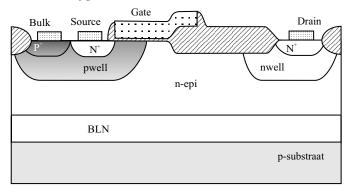

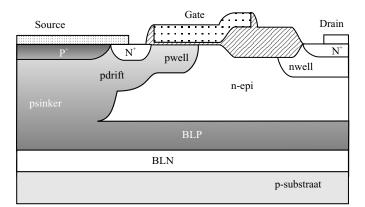

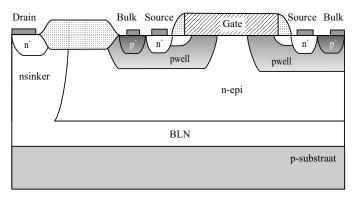

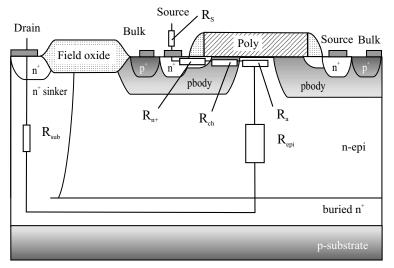

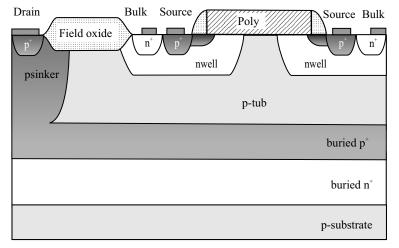

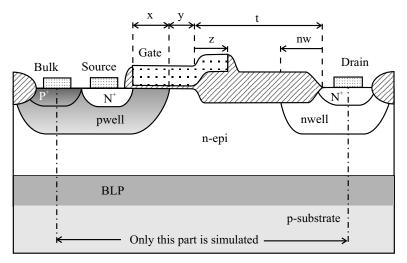

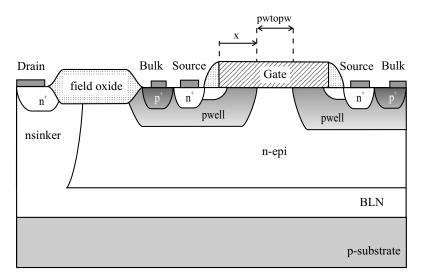

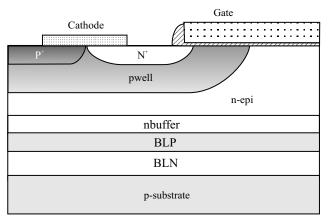

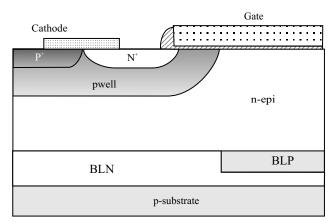

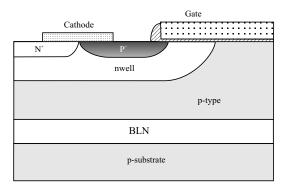

Aangezien we werken op een p-substraat, betekent dit dat voor een nVDMOS een begraven laag van het n-type (BLN), een n-plug en een n-epi nodig is (zie figuur 20). Een pVDMOS is moeilijker te realiseren omdat de drain geïsoleerd moet worden van het p-substraat zoals geschetst in figuur 14. Er zullen ook nog andere redenen aangehaald worden waarom een nVDMOS verkozen wordt boven een pVDMOS (in de paragraaf over de pLDMOS).

Figuur 14 Geïntegreerde verticale pDMOS.

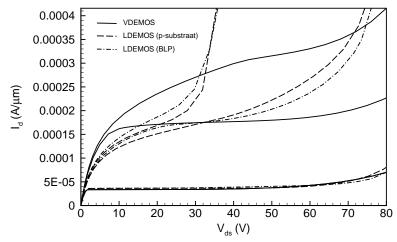

Verder kan dezelfde technologie ook nog gekozen worden voor een laterale (RESURF) nDMOS, die al dan niet-zwevend kan zijn (zie verder). Merk op dat de nVDMOS van nature uit zwevend is, wat een groot voordeel is. Een interessante vraag—die in de loop van dit hoofdstuk wordt beantwoord—is of de laterale (RESURF) nDMOS nu werkelijk beter presteert dan de verticale nDMOS.

#### **RESURF** of niet ?

Het is duidelijk dat de nVDMOS geen gebruik maakt van het RESURFeffect. De pLDMOS daarentegen zal dit wel doen (zie onder). We kunnen ook nog een laterale RESURF nDMOS ontwerpen die zowel zwevend als niet-zwevend kan zijn (zie onder).

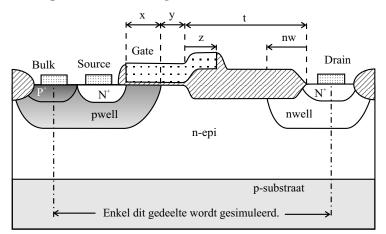

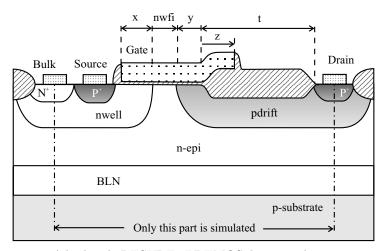

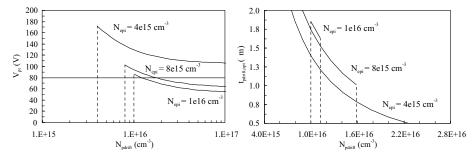

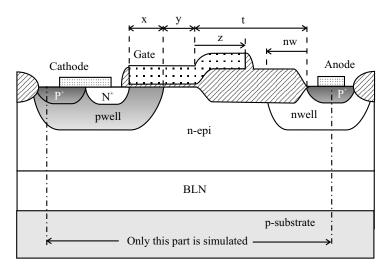

# 4.5 Niet-zwevende, laterale, RESURF nDEMOS zonder begraven lagen

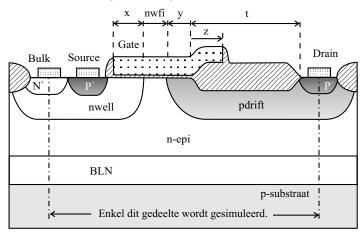

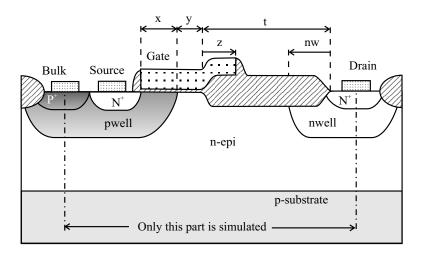

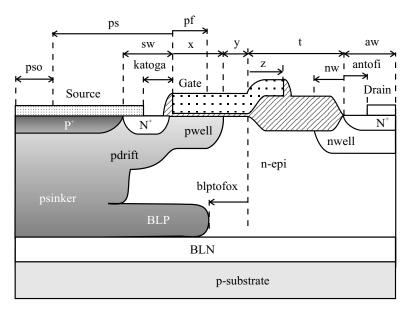

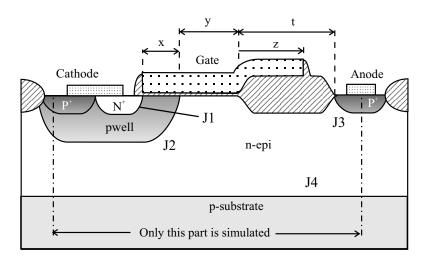

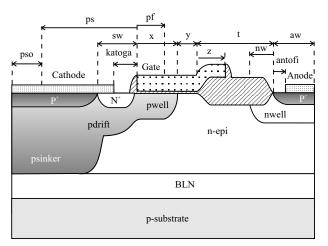

De zwevende, laterale RESURF nDEMOS wordt getoond in figuur 15 samen met de belangrijkste lay-outparameters die deze transistor beschrijven. Het p-substraat is lager gedopeerd dan de n-epilaag en dus kan hier het "ware" RESURF-effect optreden. Daarmee wordt bedoeld dat bij optimale RESURF-condities (in de eerste plaats een optimale n-epidosis en in de tweede plaats een  $t > t_{epi}$ ) het p-substraat de doorslagspanning zal bepalen. Deze ligt ver boven de 80 V die door de I3T80-technologie wordt opgelegd vanwege het lage doperingsniveau van het substraat en dit voor een groot bereik van epidiktes en -concentraties.

Figuur 15 De niet-zwevende, laterale RESURF nDEMOS met belangrijkste lay-outparameters.

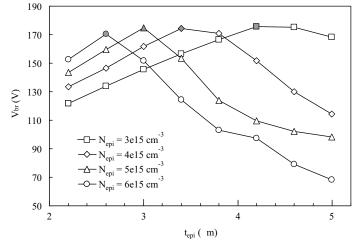

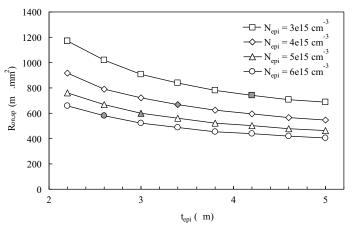

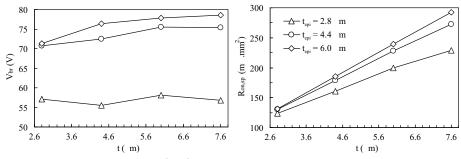

Wanneer deze transistor geschaald moet worden naar 80 V, dan is de enige oplossing een verkleining van de lay-outparameter t. Wanneer we

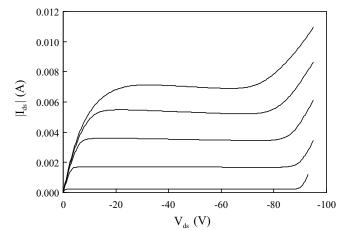

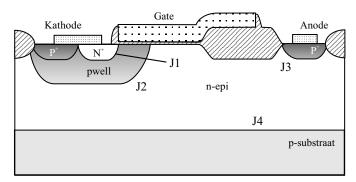

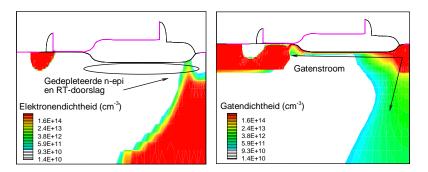

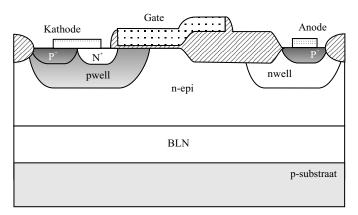

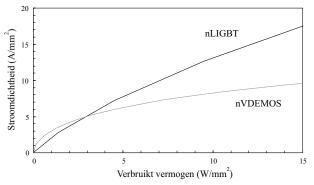

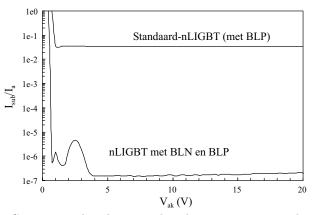

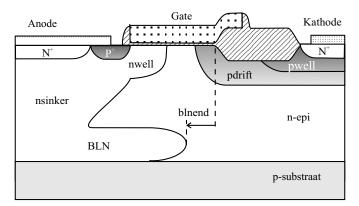

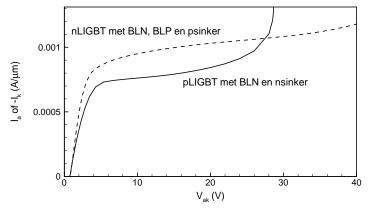

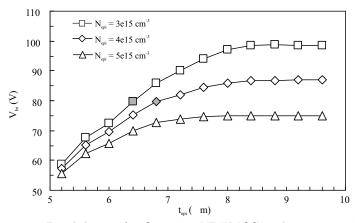

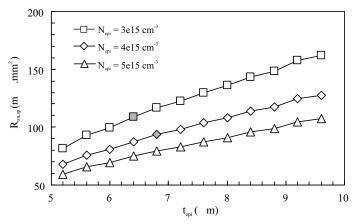

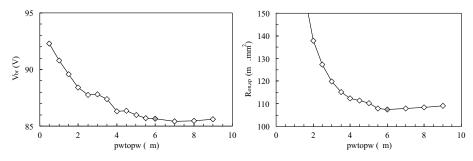

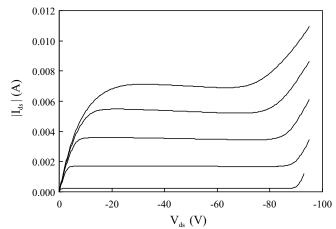

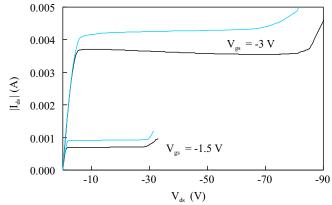

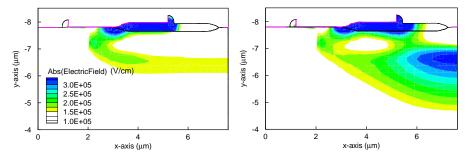

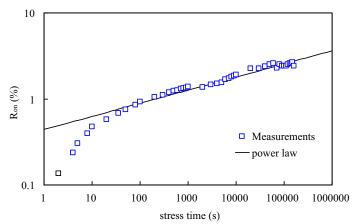

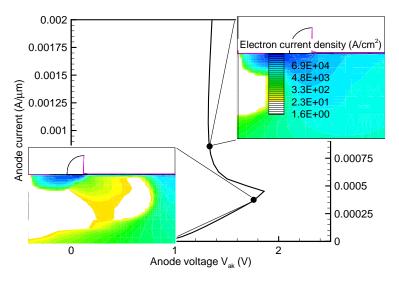

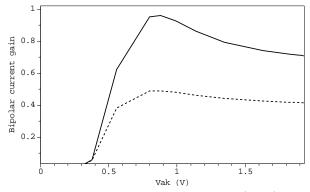

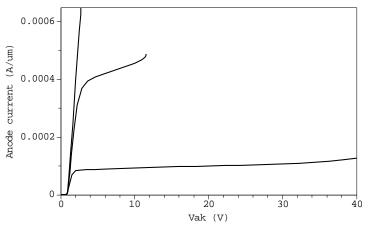

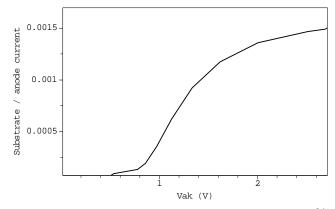

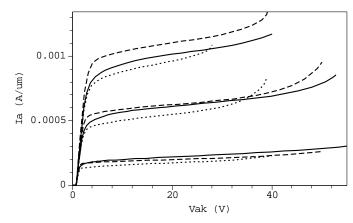

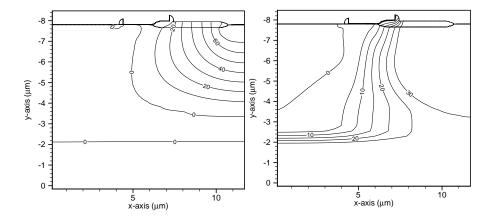

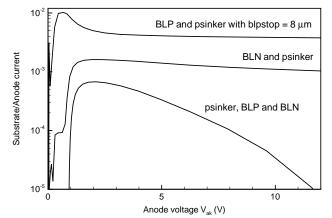

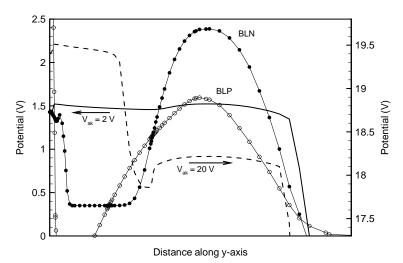

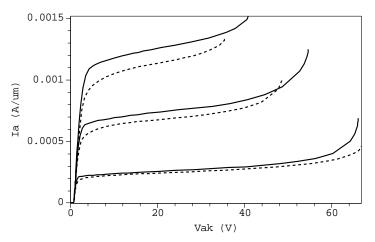

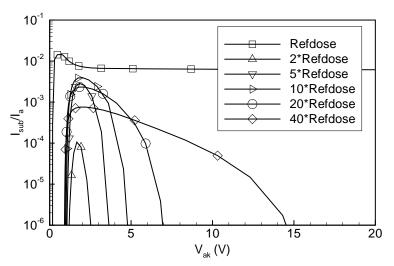

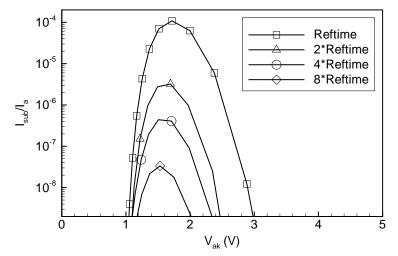

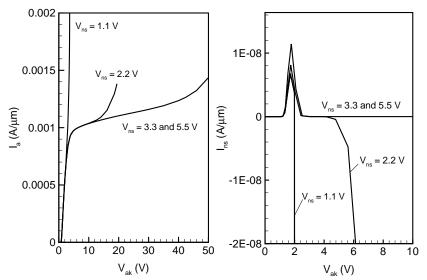

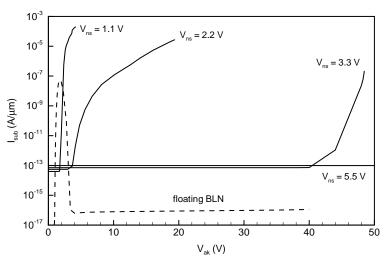

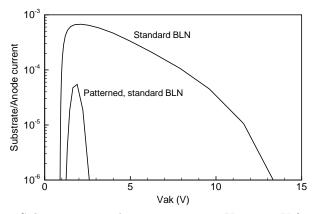

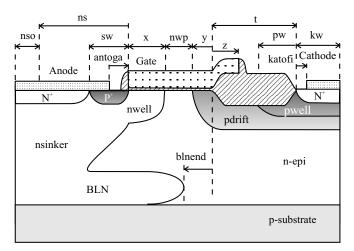

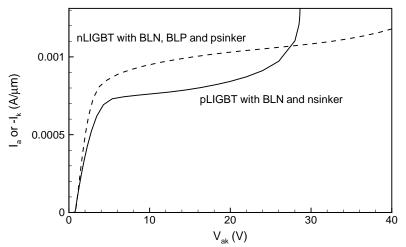

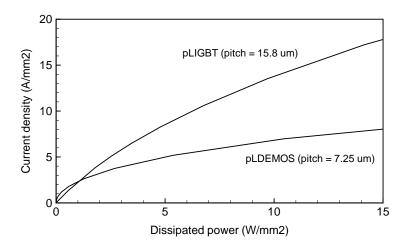

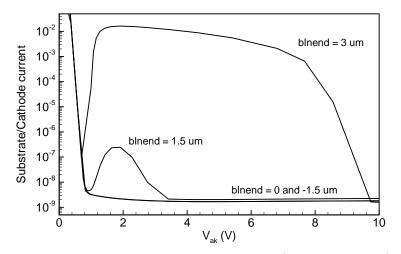

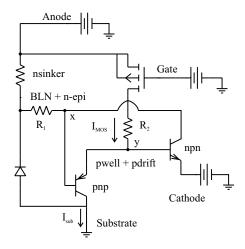

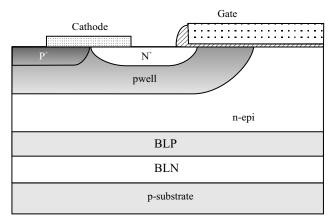

dit doen voor verschillende epilagen, dan zien we dat er een optimum is. Dit komt omdat hoe hoger het doperingsniveau van de epilaag is, hoe dunner de epilaag moet zijn om aan de optimale RESURF-condities te blijven voldoen. Nu heeft een dunner wordende epi in eerste instantie weinig invloed op de aan-weerstand daar een groot deel van de stroom toch net onder de SiO<sub>2</sub>-grensoppervlak stroomt. De hogere concentratie aan ladingsdragers in de epilaag zal dus een sterkere invloed hebben dan de dunnere epilaag. Bij een bepaalde concentratie wordt de epilaag echter zo dun, dat de aan-weerstand opnieuw stijgt (zie tabel 1).